공부한 지 한참 돼서 가끔 헷갈릴 때가 있습니다

그중 CPU 관련 설명을 우연히 유튜브 영상 접했는데

그림으로 잘 설명되어 있고 회로 레벨부터 전반적으로 조립해주니 재밌네요

마침 연구실에서 센서네트워크 노드 땜질하면서

궁금해서 찾아봤던 정리해두었던 내용과 겹치기도 해서

영상 내용에 개인적으로 정리한 내용 보충하여 새로 정리해봅니다

CPU

- Central Processing Unit

- 중앙 처리 장치

- 기억, 해석, 연산, 제어 수행

CPU와 RAM은 반도체로 구성됩니다

- 도체 : 비저항이 작아 전기가 잘 통하는 물체

- 부도체 : 비저항이 높아 전기가 잘 통하지 않는 물체

- 반도체 : 도체와 부도체의 중간 정도로 전기가 통하는 물체

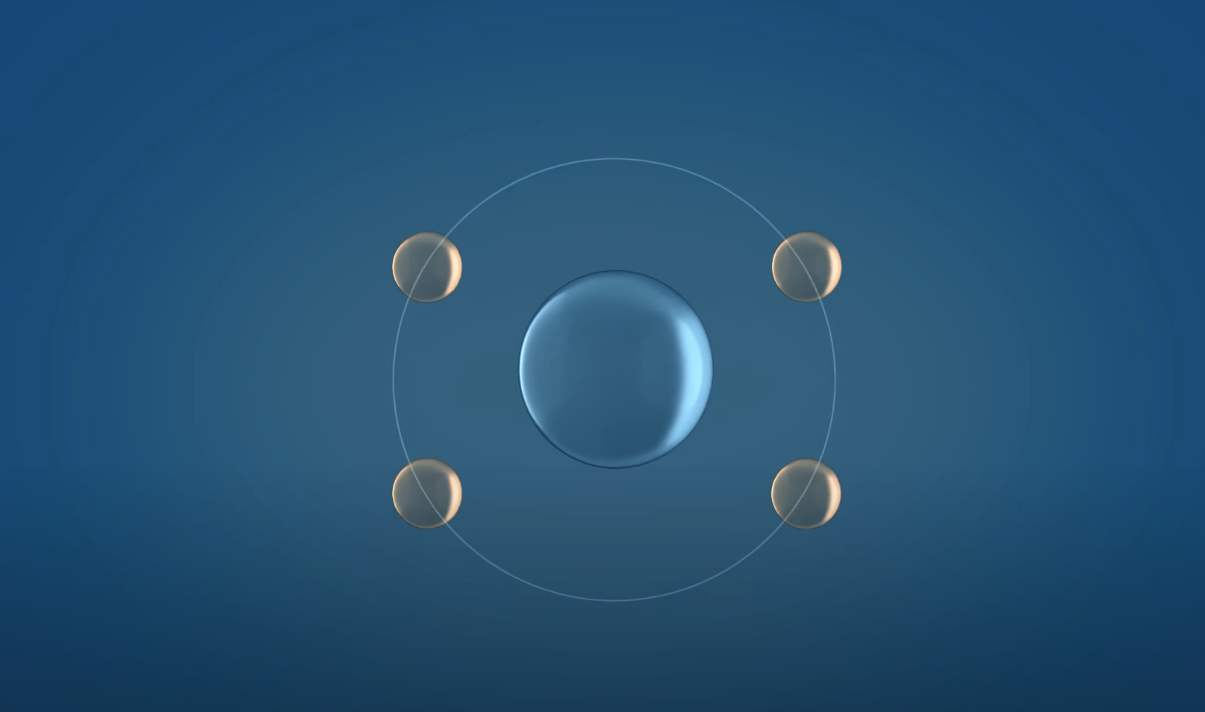

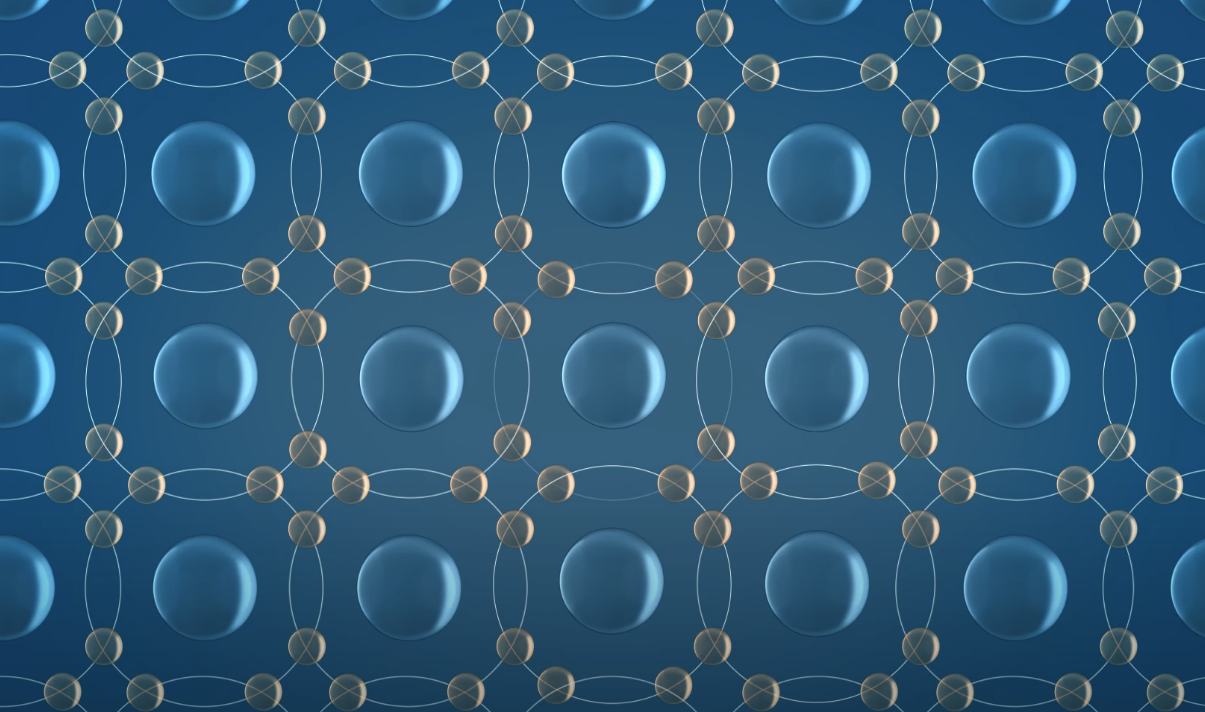

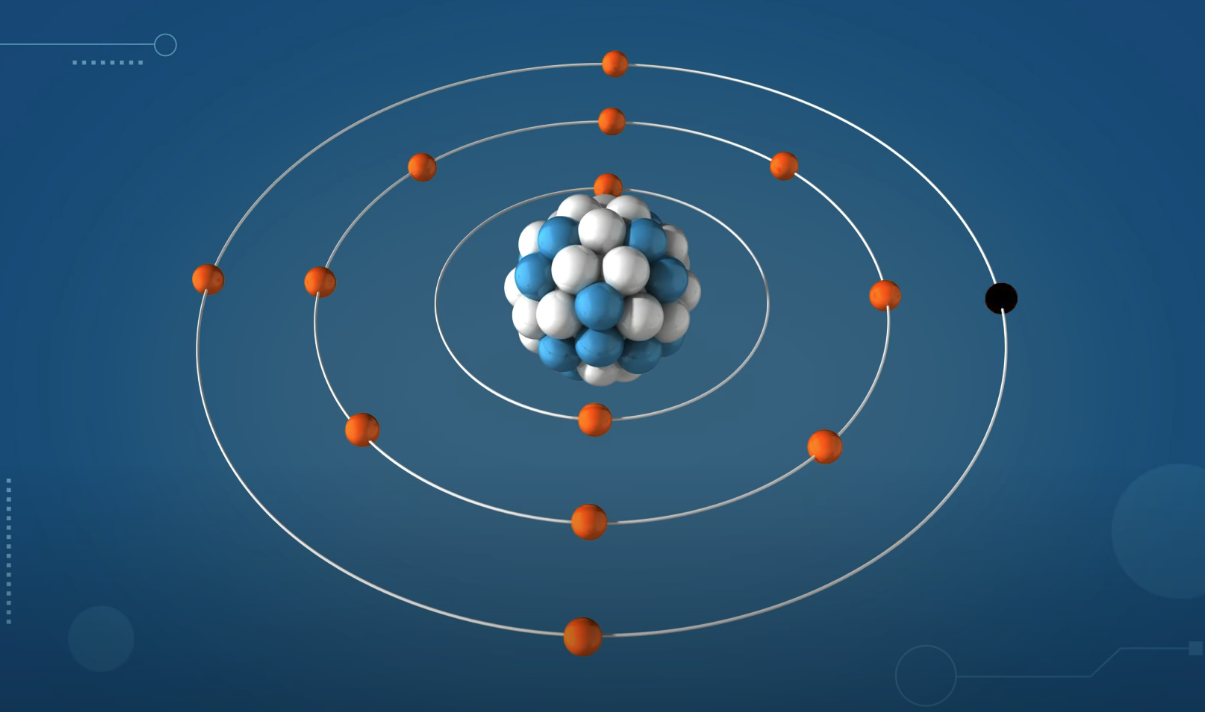

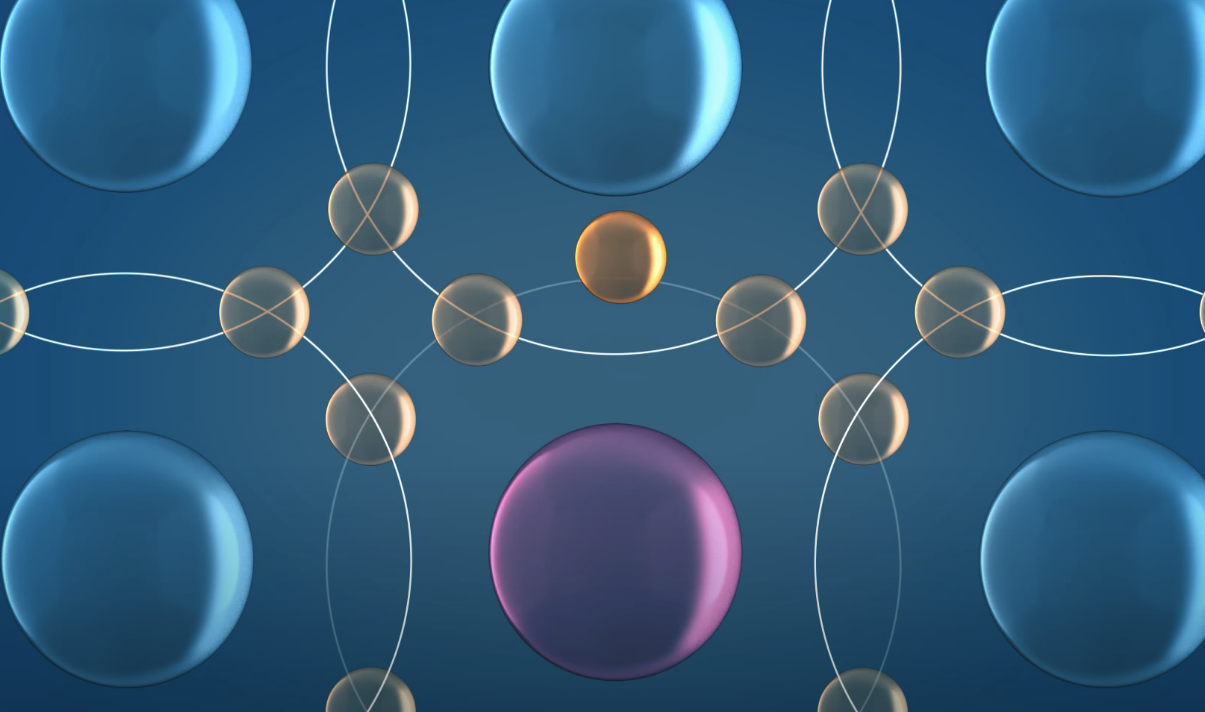

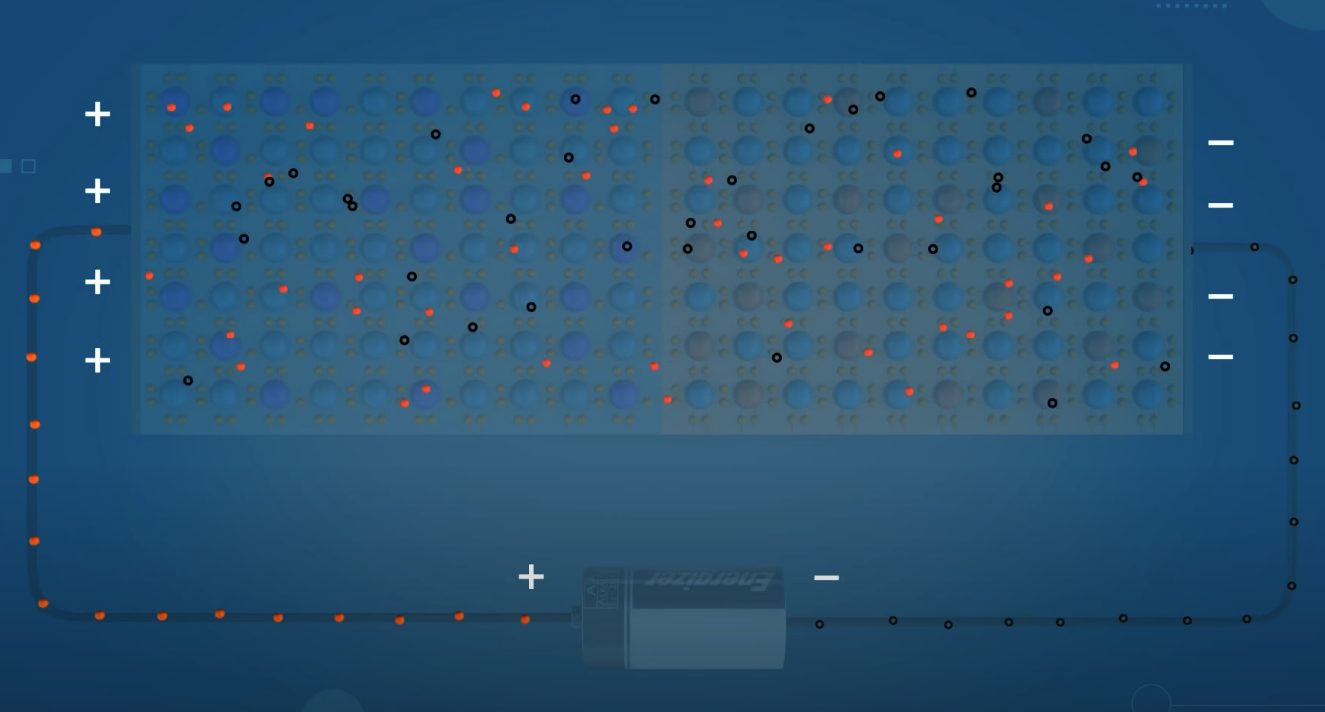

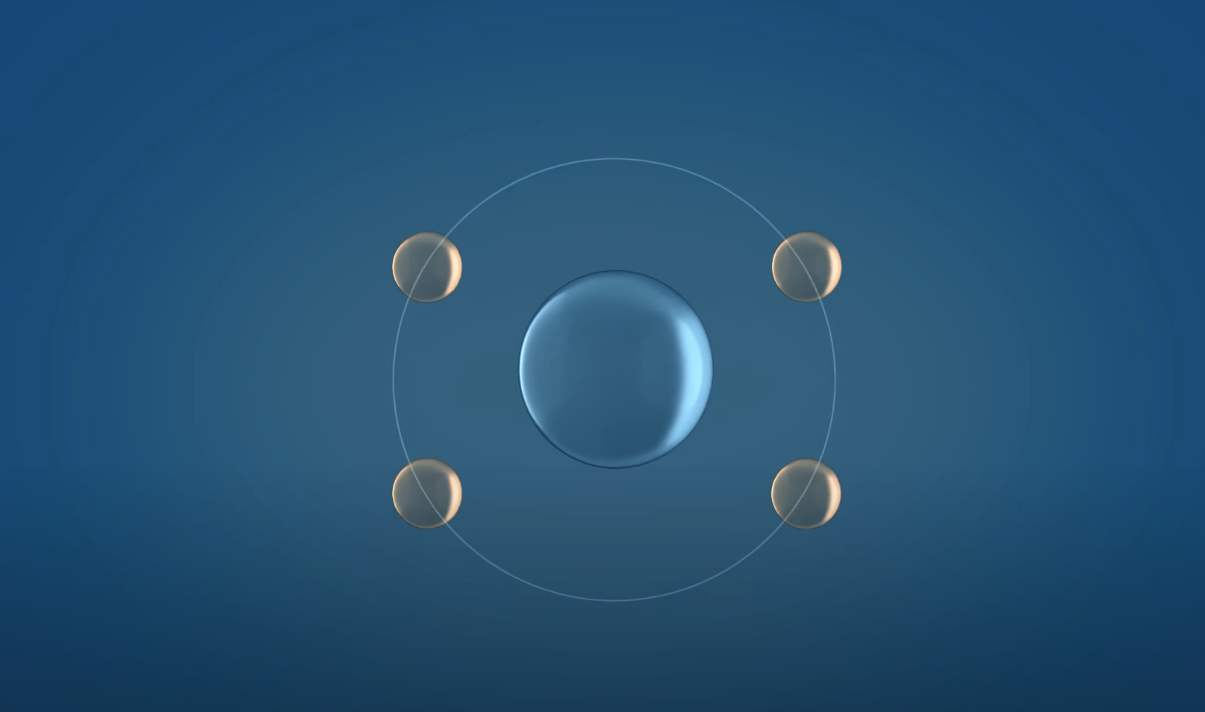

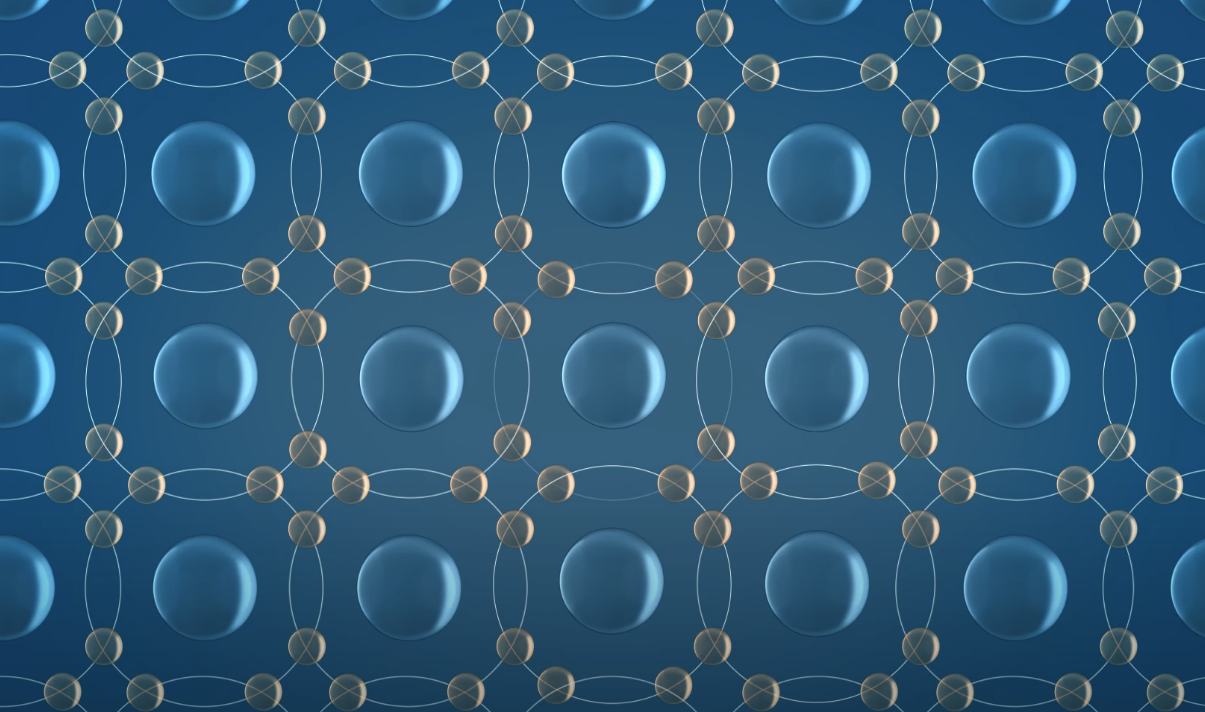

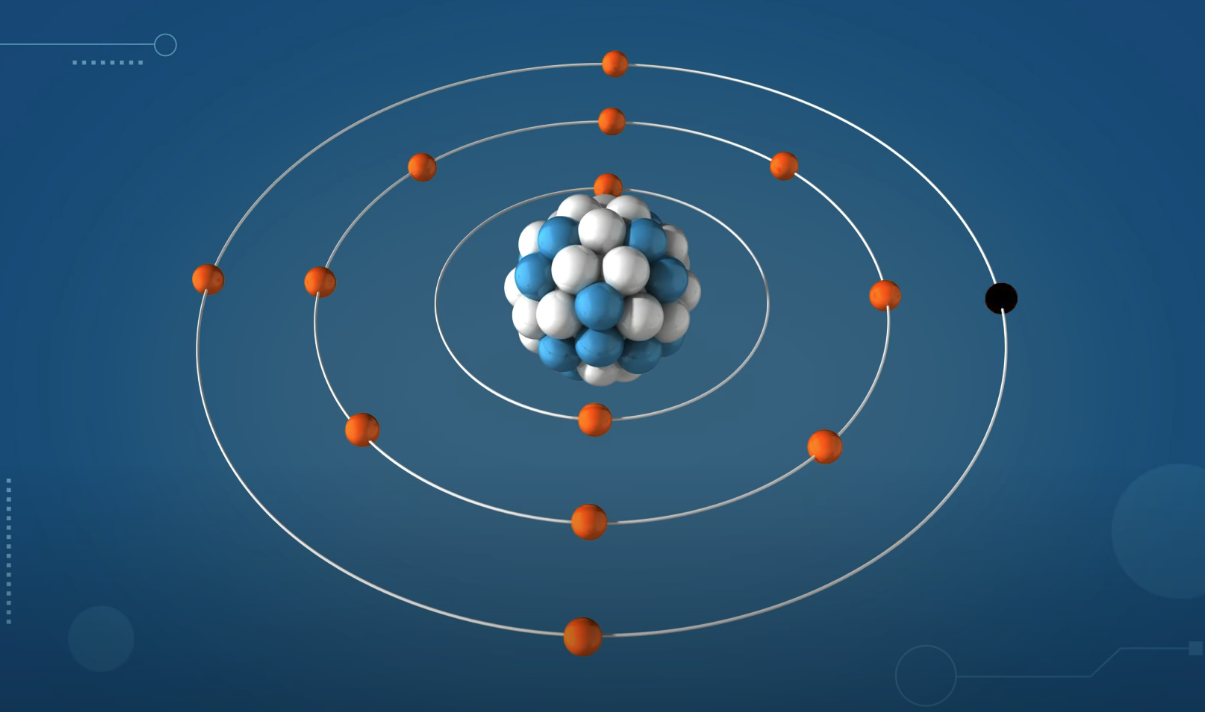

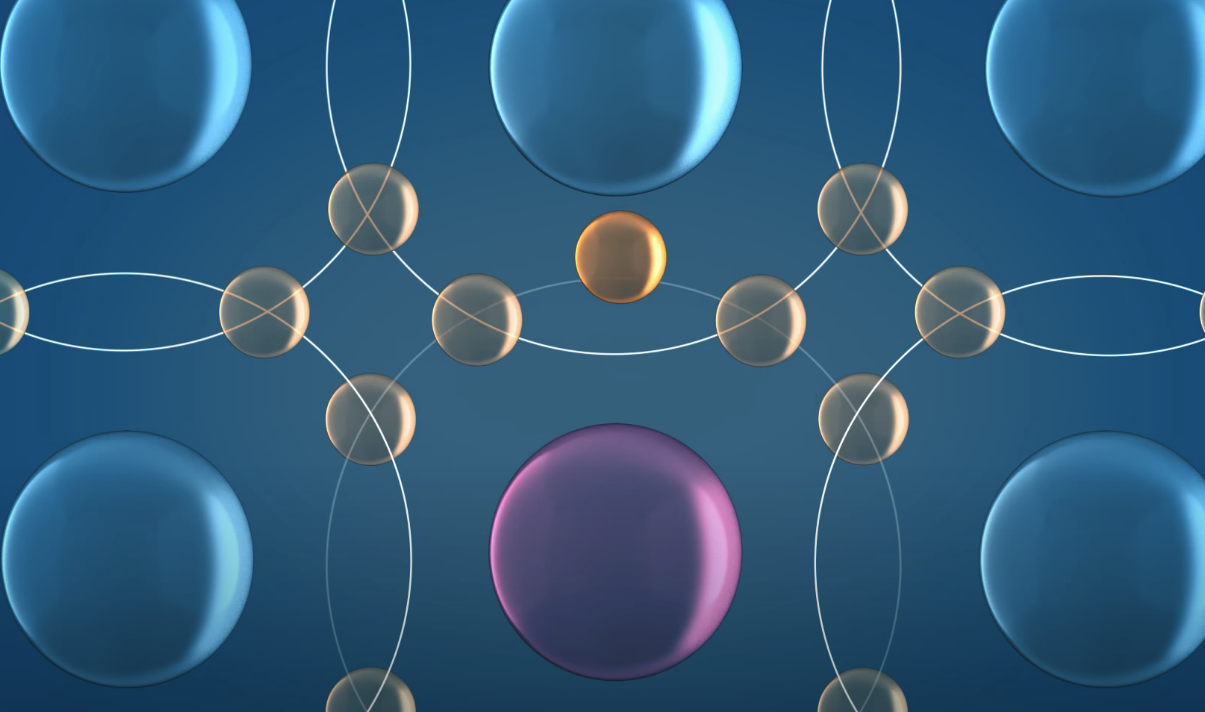

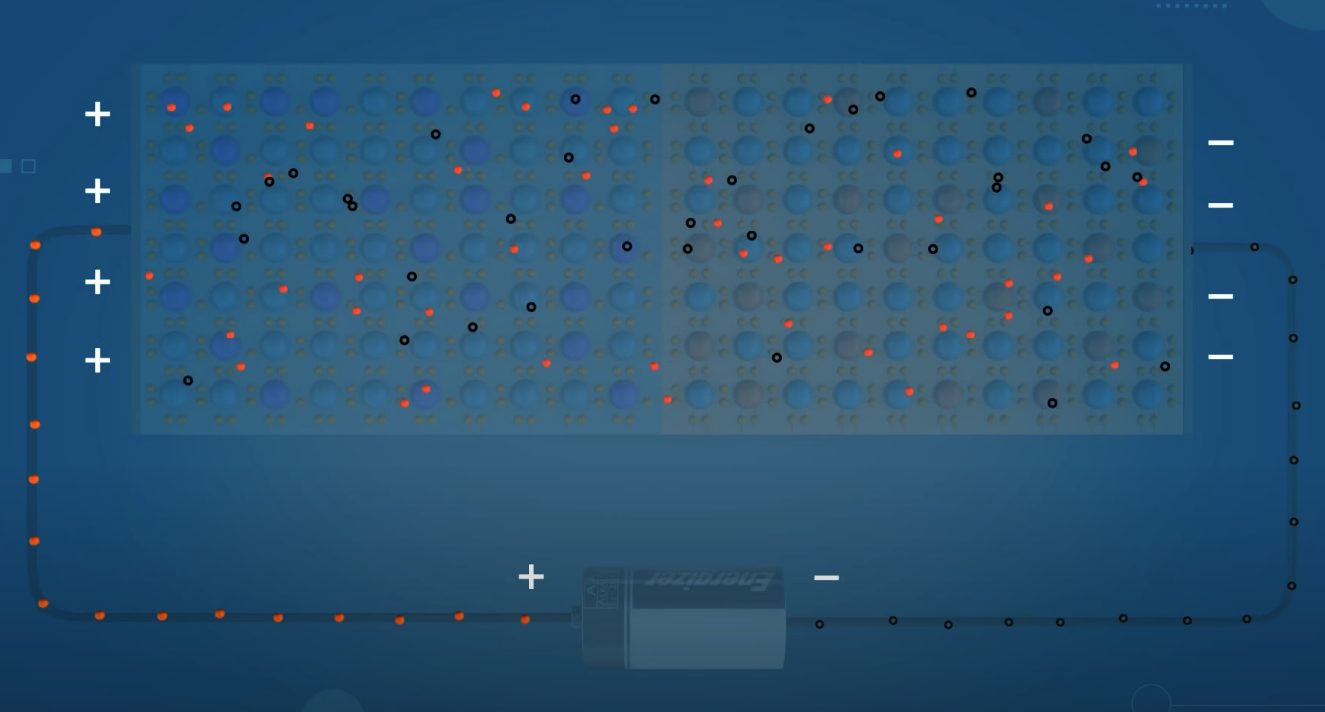

반도체는 주로 실리콘으로 구성

실리콘은 최 외각 전자가 4개

다른 실리콘 원자들과 전자를 공유하며 단단하게 결합됨

원자는 최 외각 전자가 8개 일 때 가장 안정적인 구조임

서로 안정적으로 단단하게 결합되어 있으면 전자가 이동하지 않음 => 전류가 흐르지 않음

즉, 순수한 실리콘은 전류가 통하기 어려움

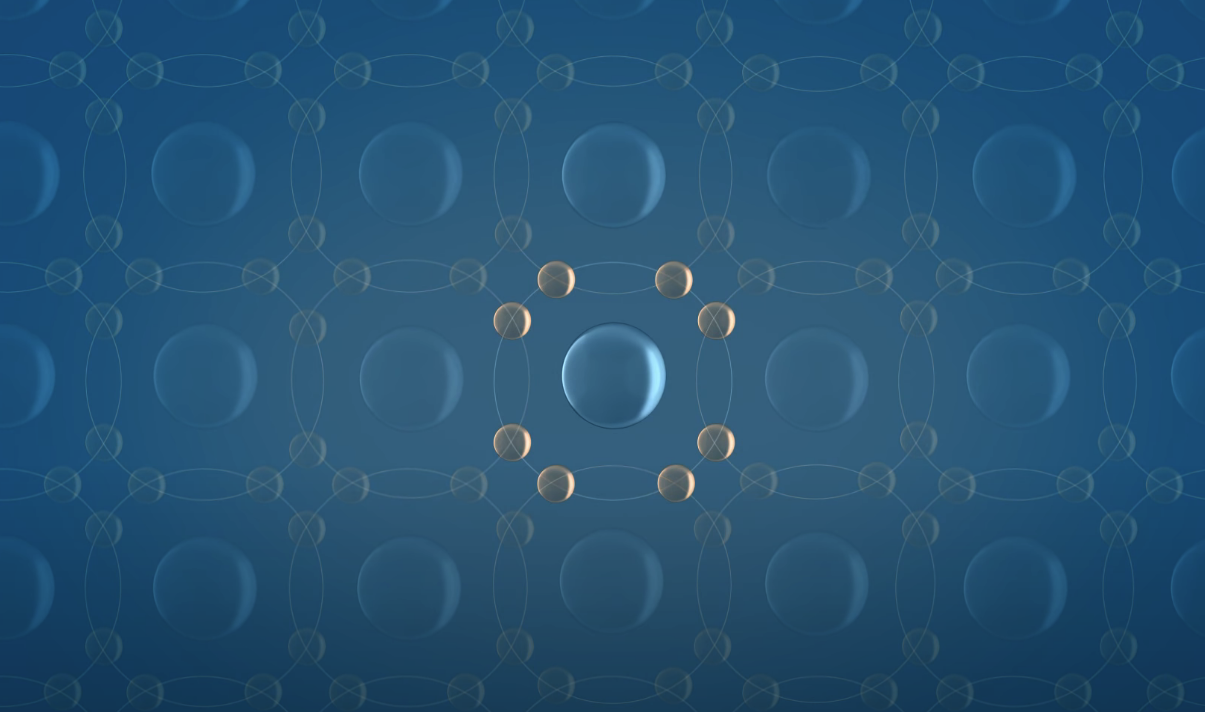

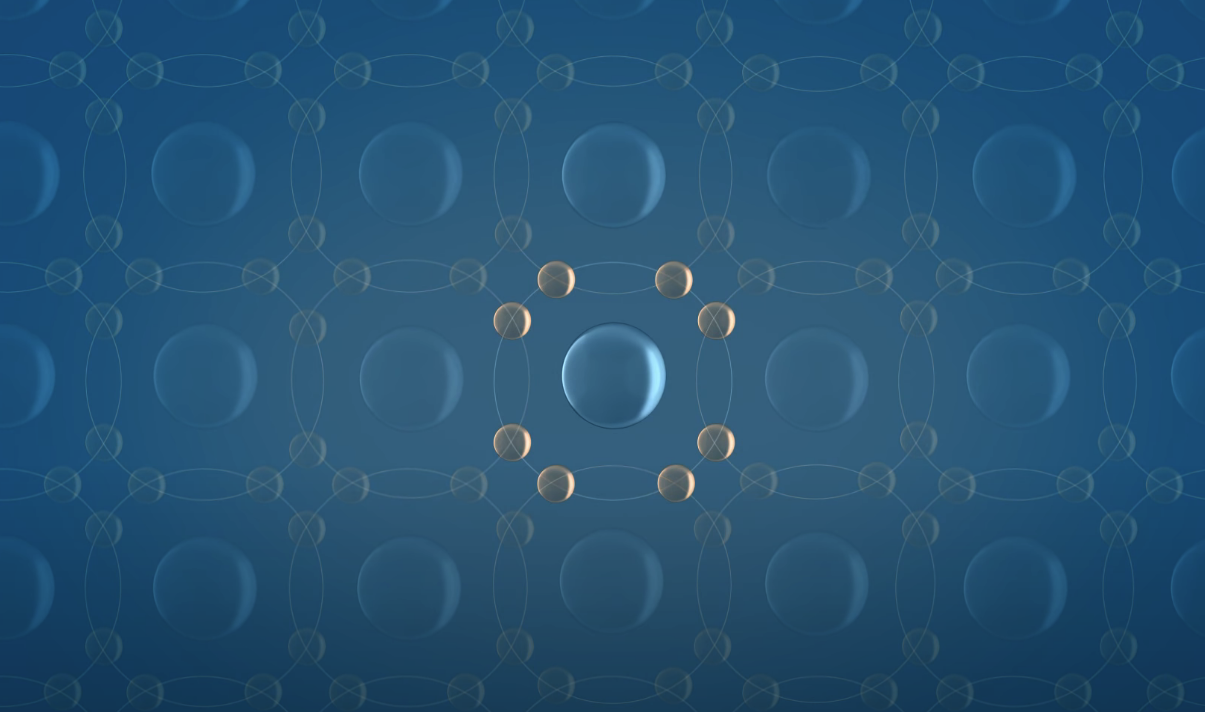

때문에 실리콘보다 전자가 많거나 적은 원소를 첨가해 전류를 통하게 만들어줌

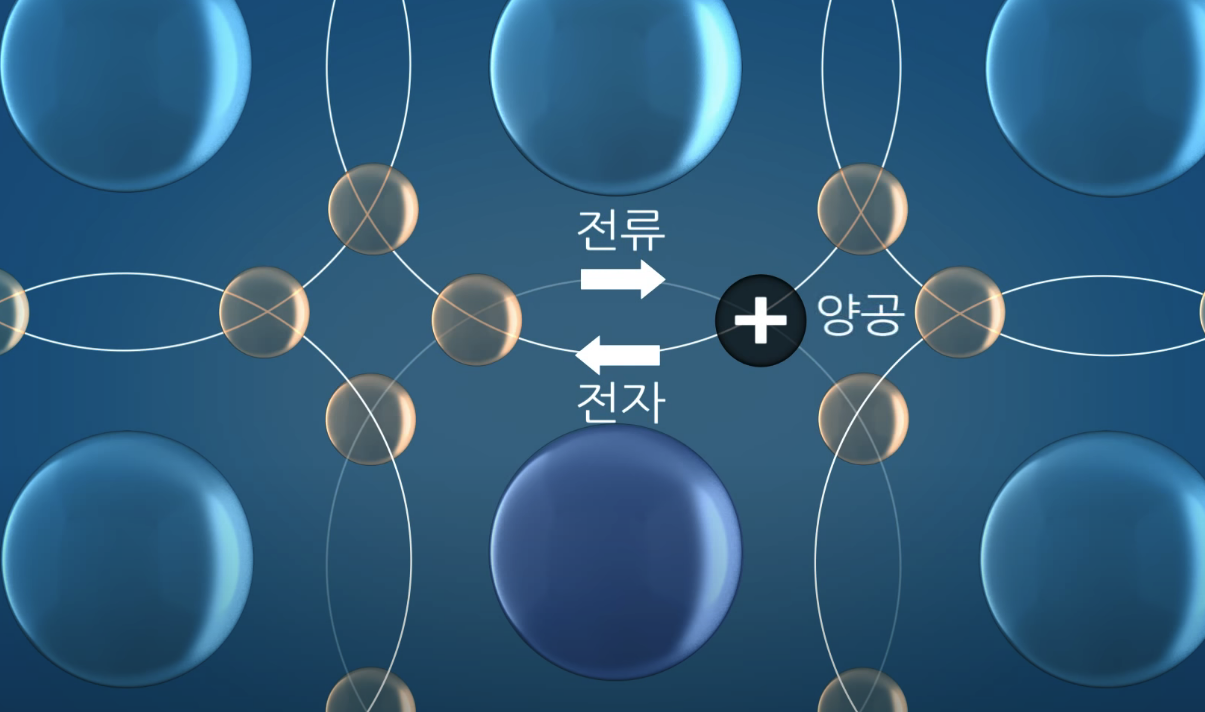

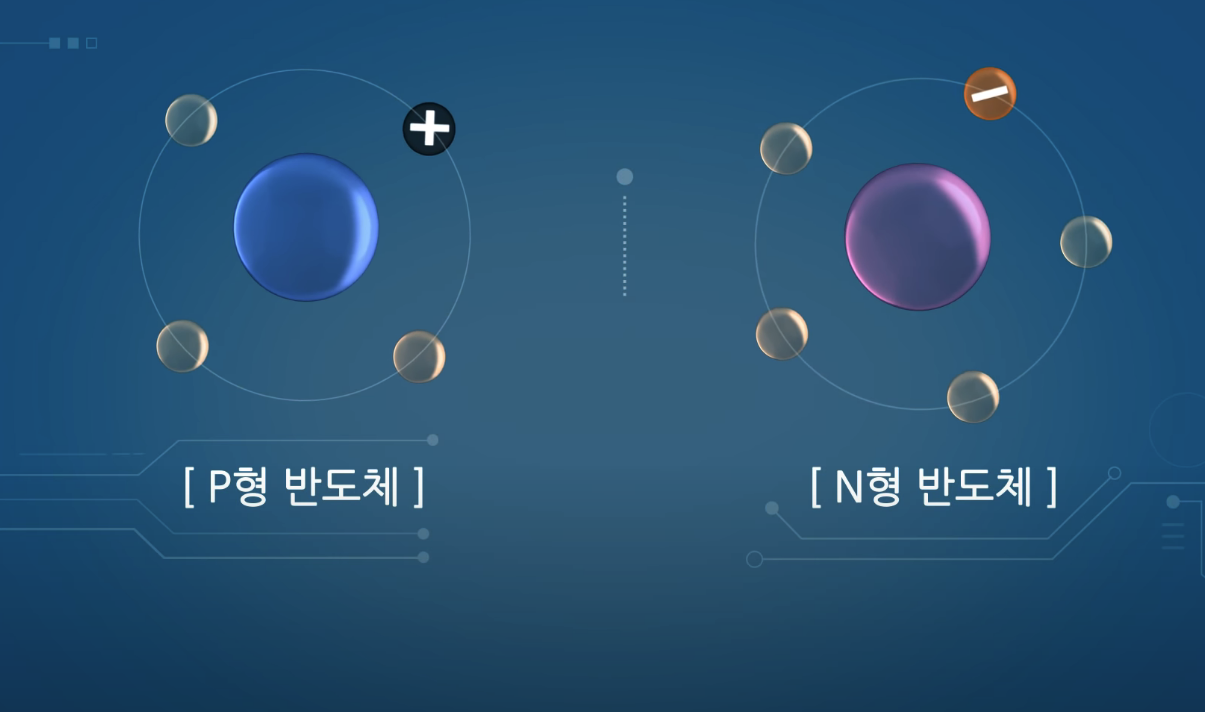

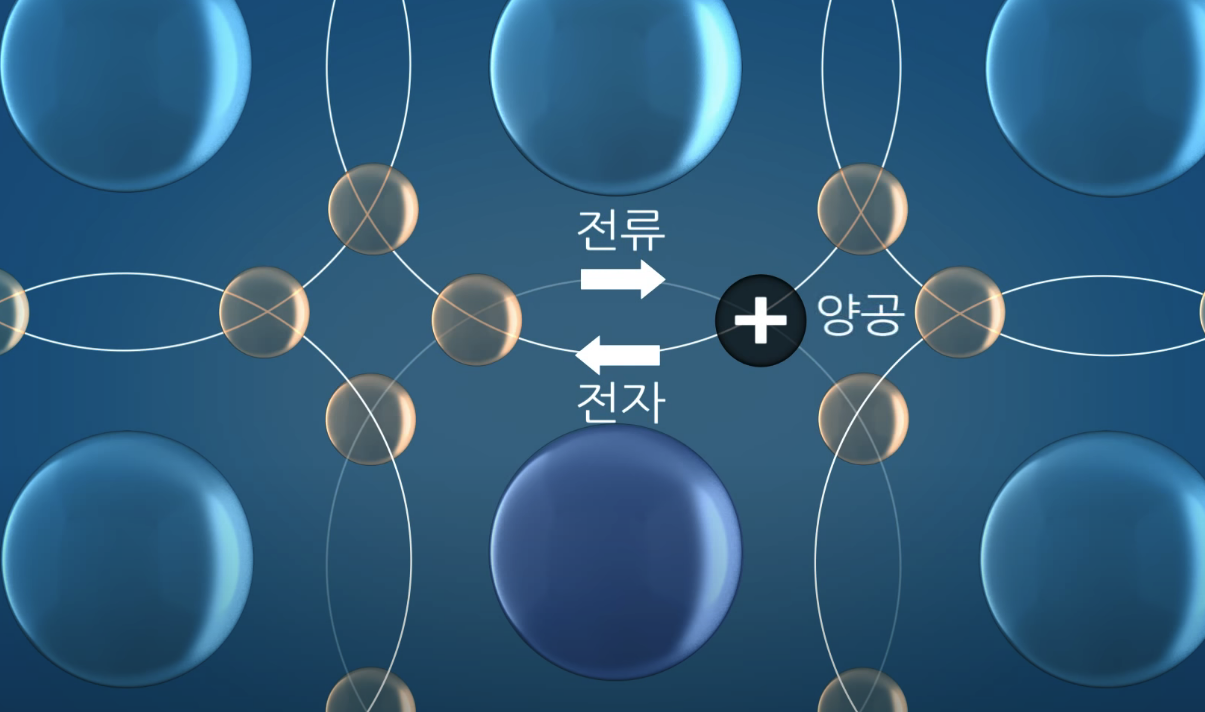

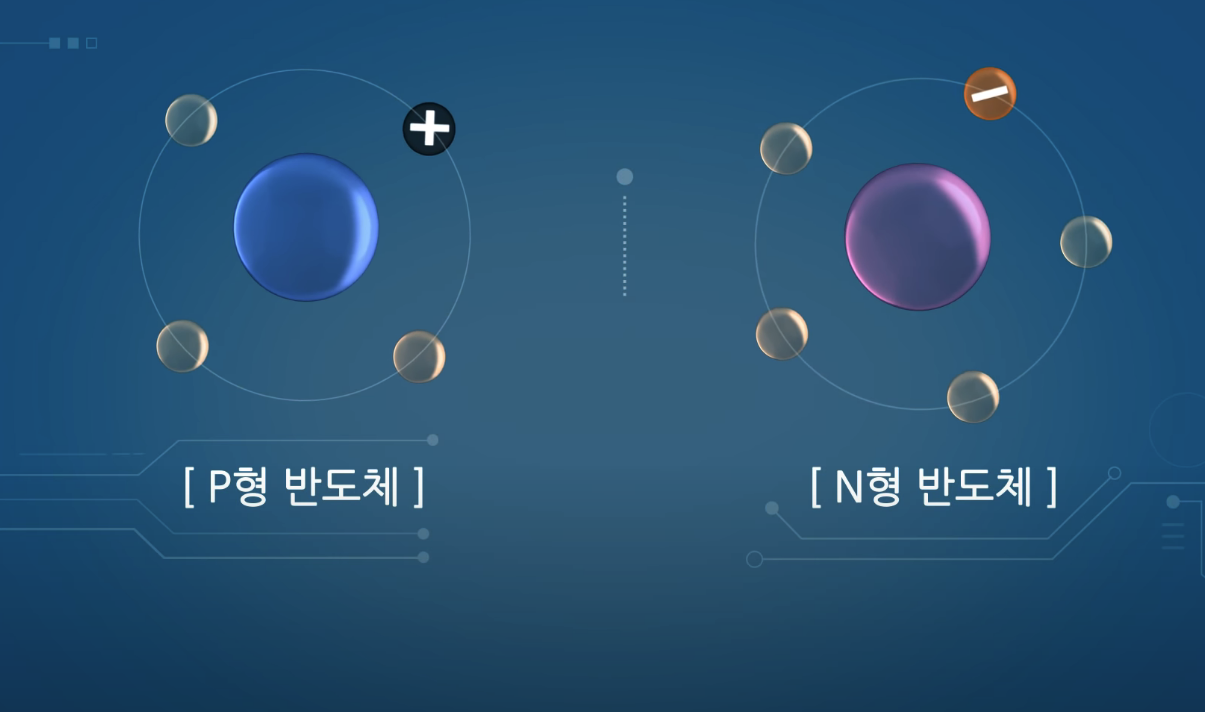

실리콘에 전자가 적은 원소를 첨가하면, 존재하는 전자들이 빈 곳으로 이동하며

전자의 이동 방향과 반대 방향으로 전류가 흐름

- 양공 : 양전하를 띈 구멍

실리콘에 전자가 한 개 많은 원소를 첨가하면, 남는 전자가 자유롭게 이동하며 전류가 흐름

전자가 많은 원소는 P(positive) 형 반도체

전자가 적은 원소는 N(negative) 형 반도체

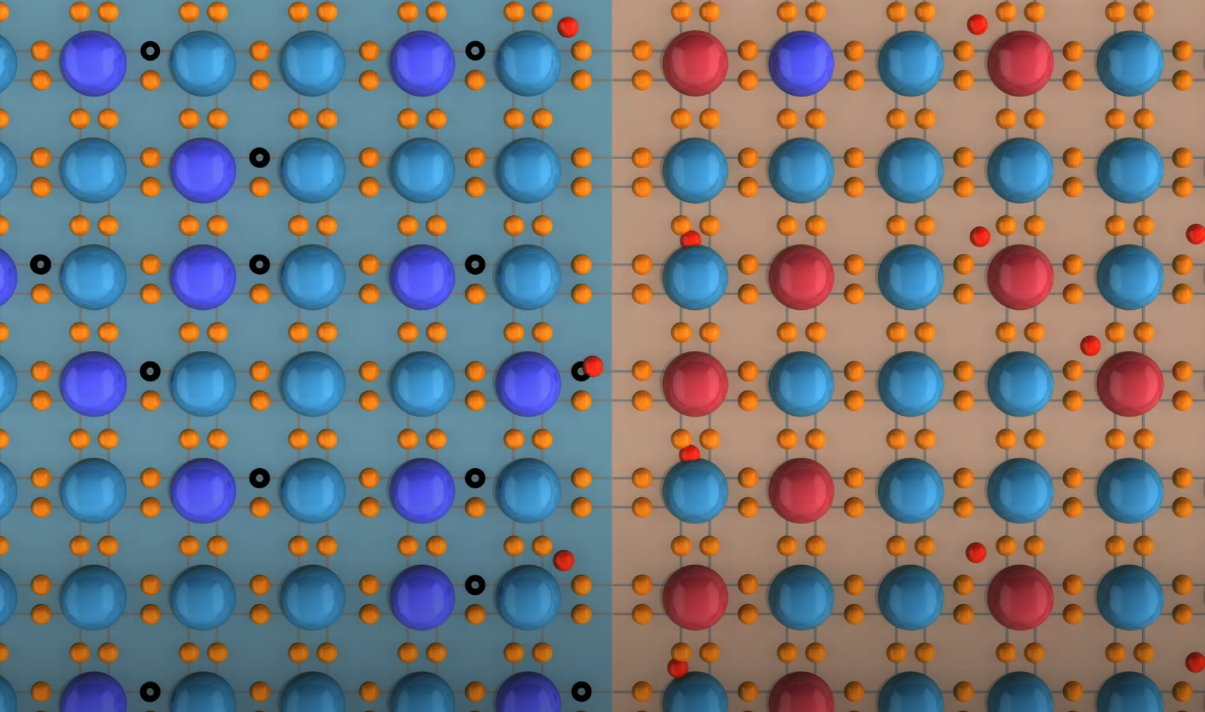

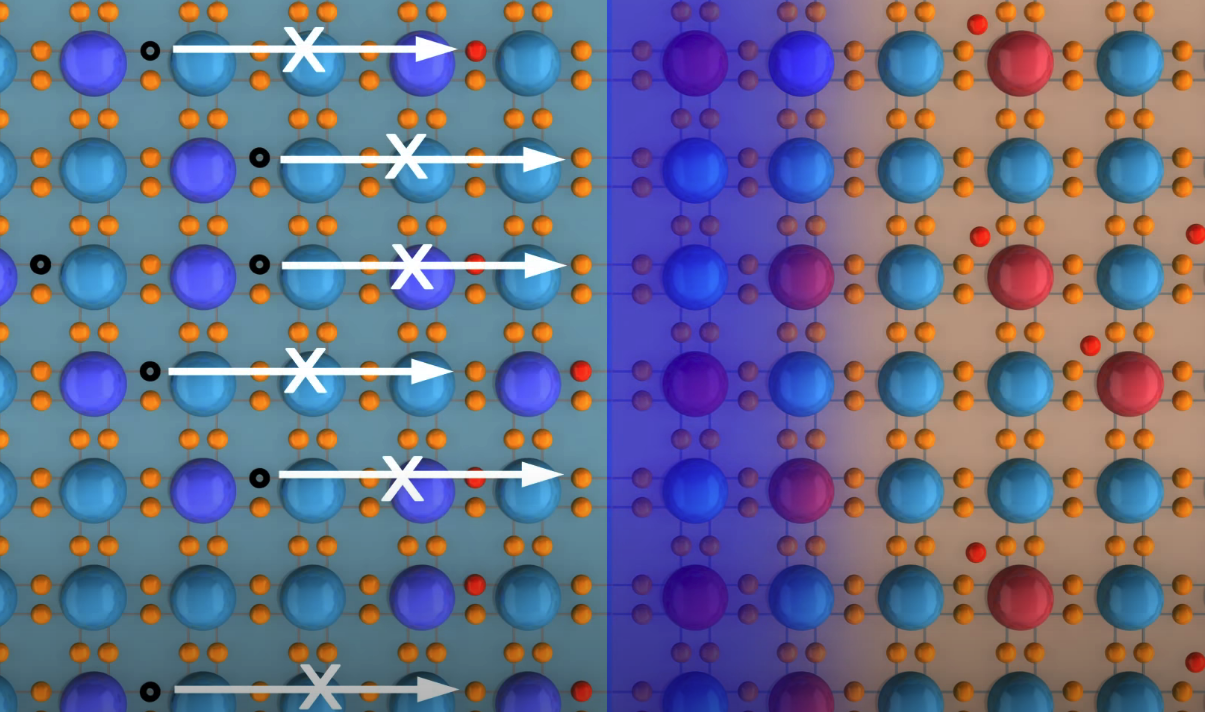

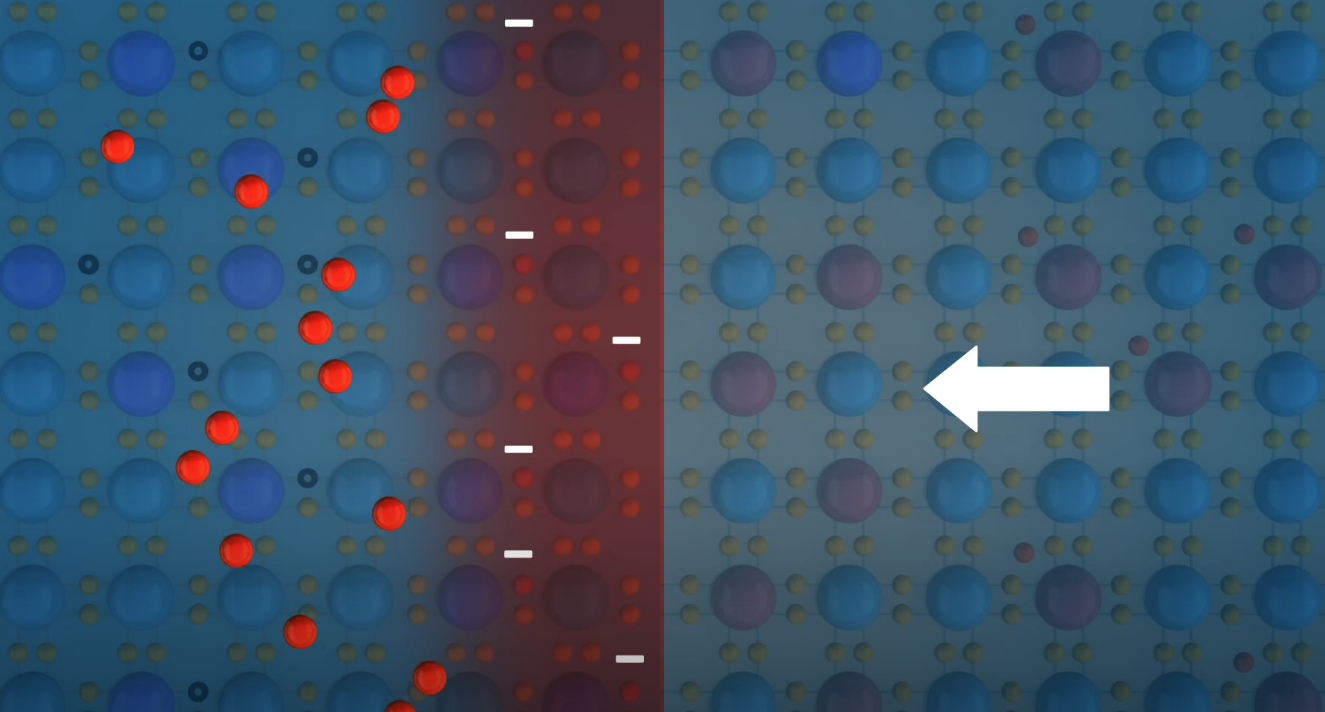

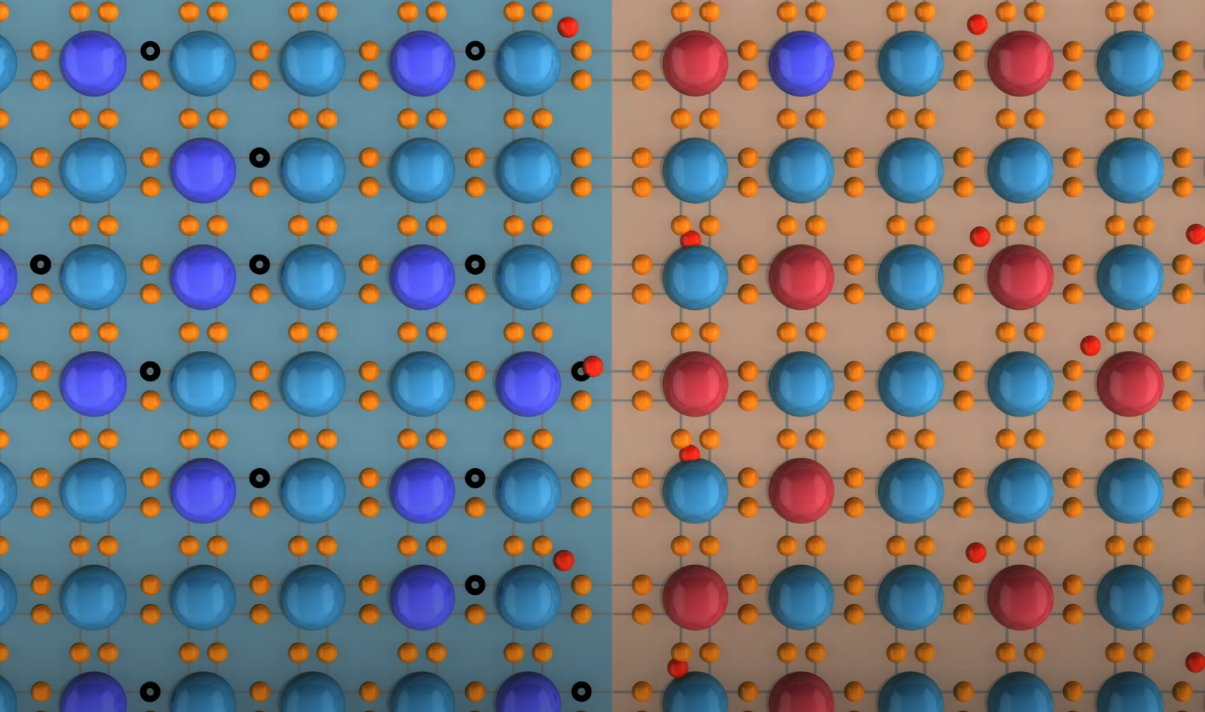

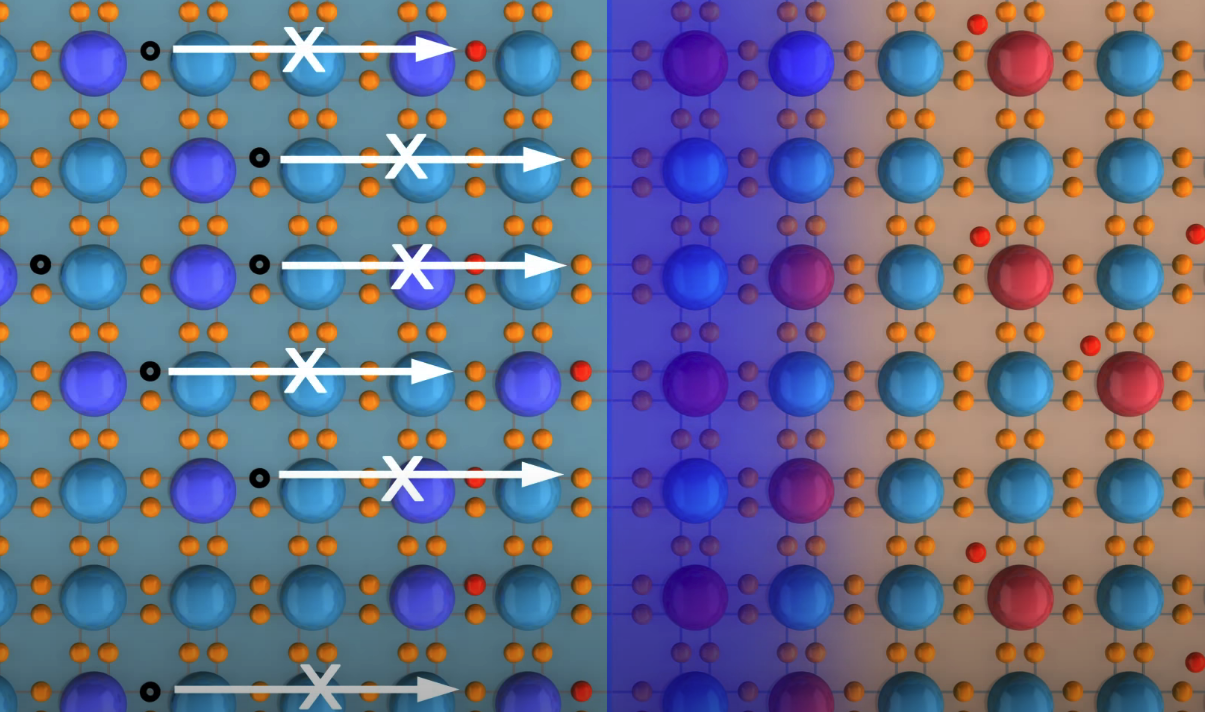

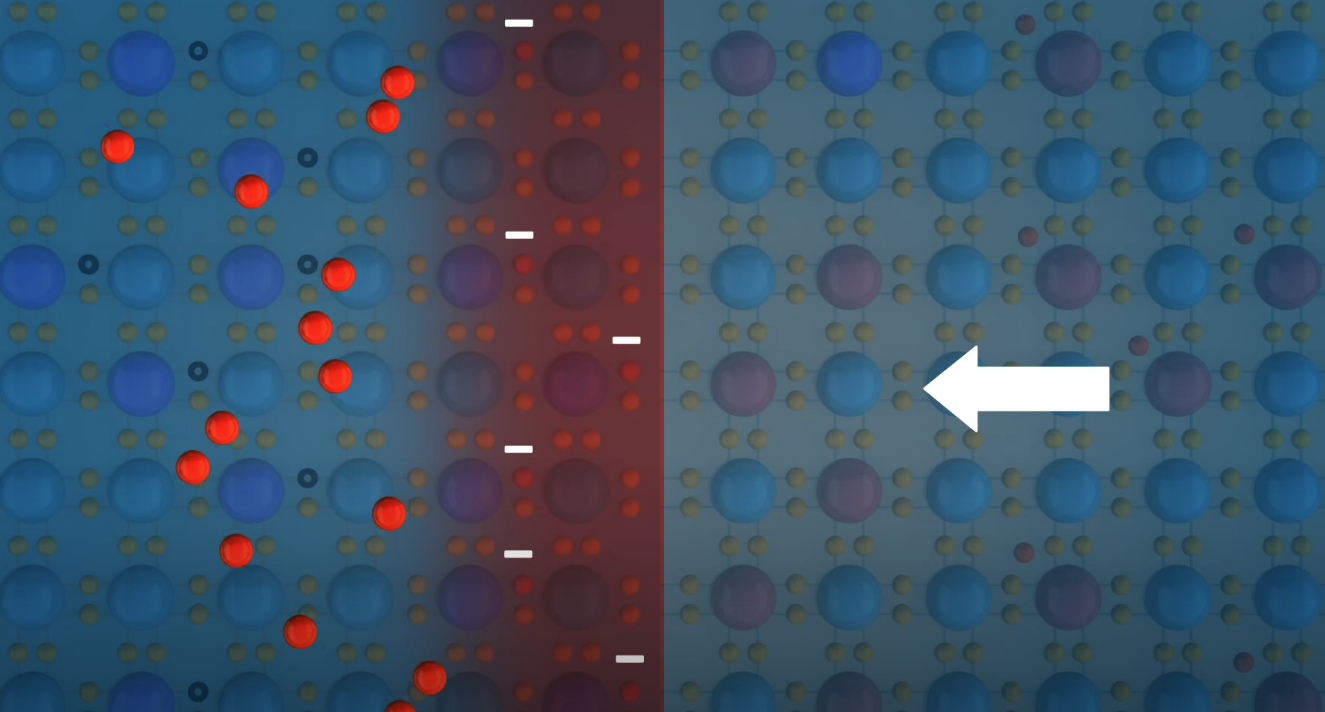

P형과 N형 반도체 둘을 연결하면 N형의 남는 전자가

P형의 양공에 끌려 결합하게 됨

중성 상태로 시작한 P형 반도체 중 전자와 결합된 원자는 음전하가 됨

일정 순간부터 음전하 벽이 생겨 더 이상 전자가 넘어오지 못함

중성 상태로 시작한 N형 반도체 중 전자를 잃은 원자는 양전하가 되며

일정 순간부터 양전하 벽이 생겨 양공이 넘어오지 못함

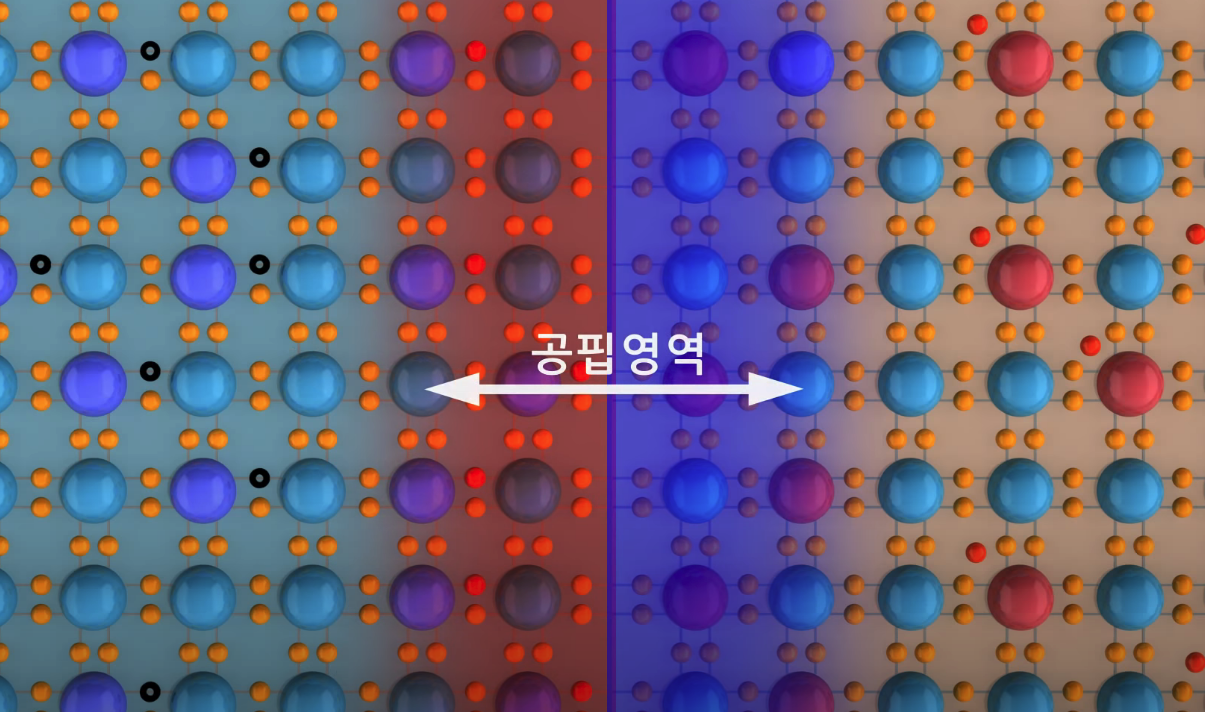

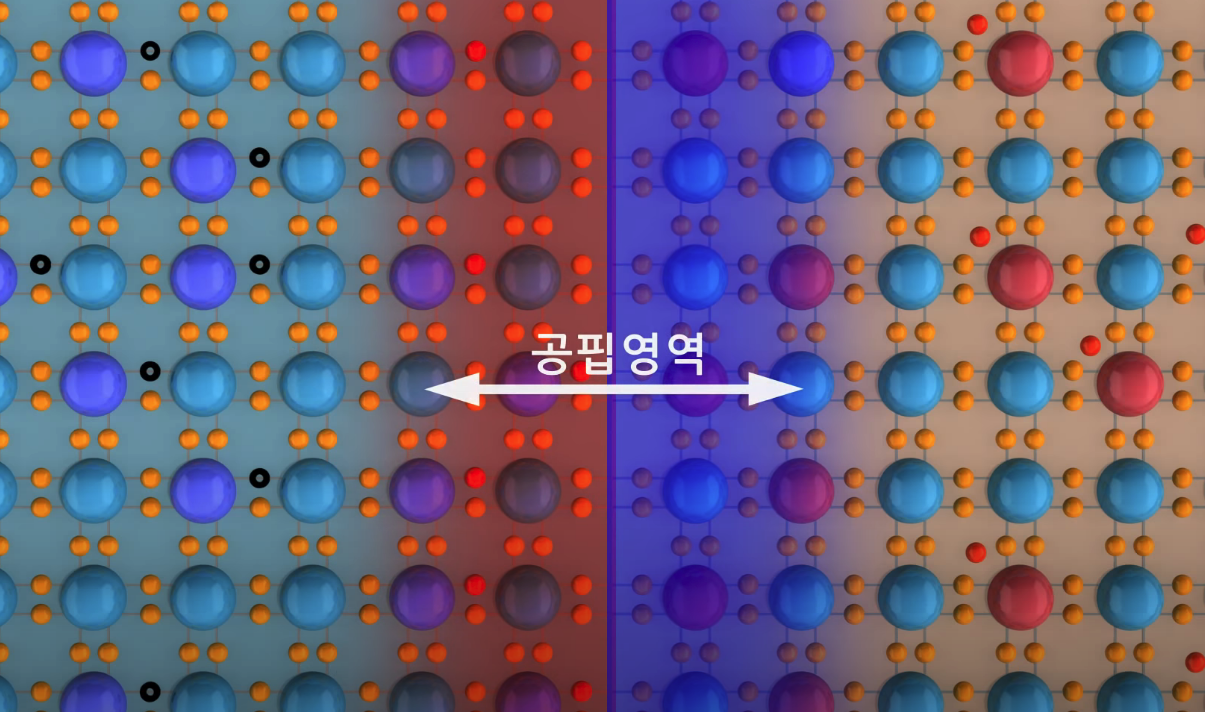

이동 가능한 전자들이 없어지고 이를 공핍 영역이라 함

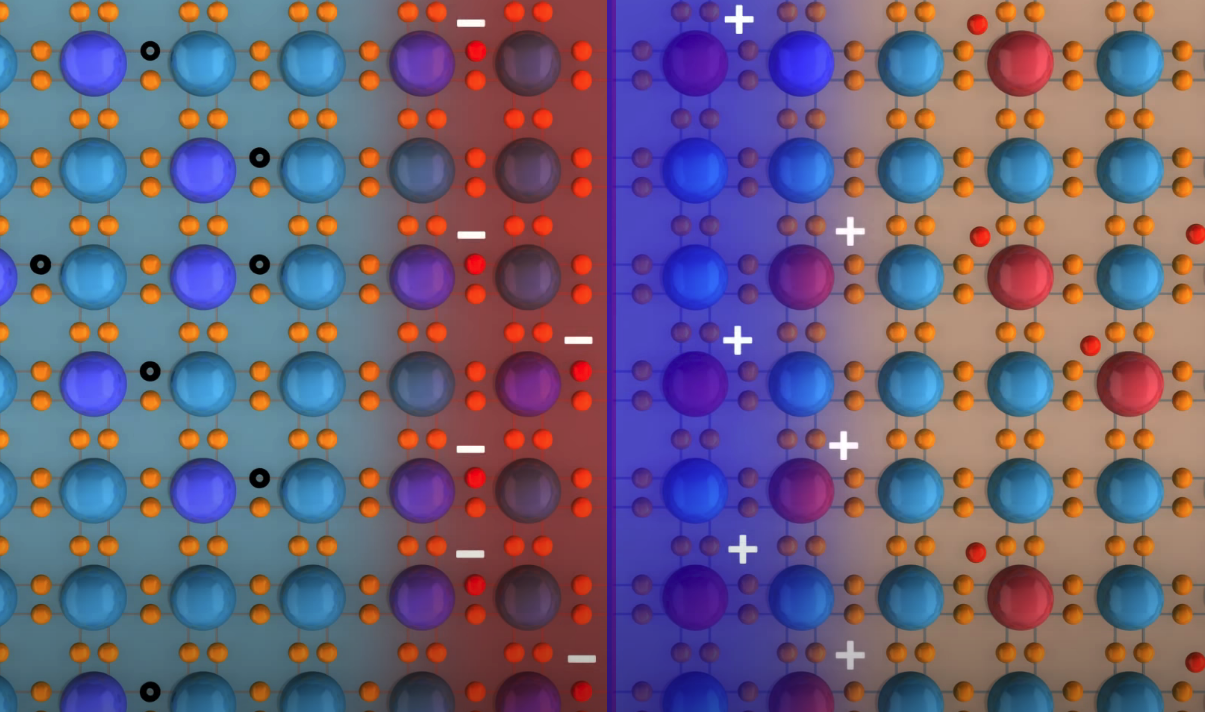

공핍 영역 가장자리에 서로 다른 전하를 가진 면이 생기고

+에서 -로 전기장이 생성됨

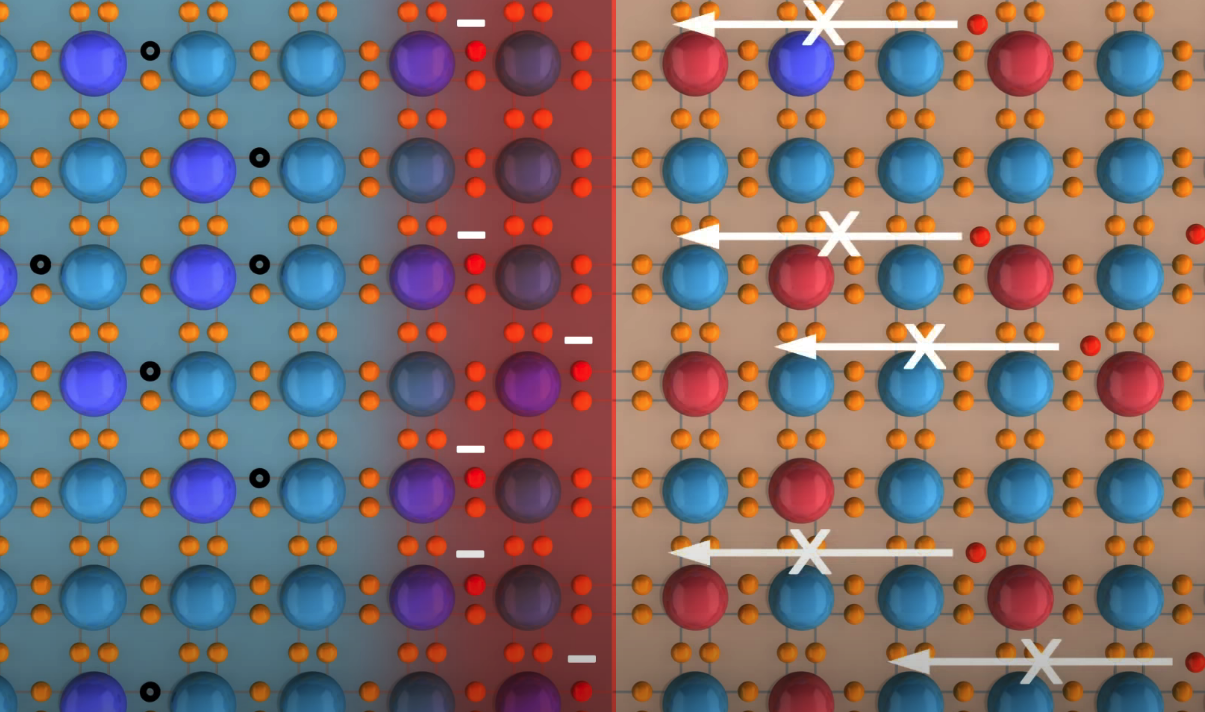

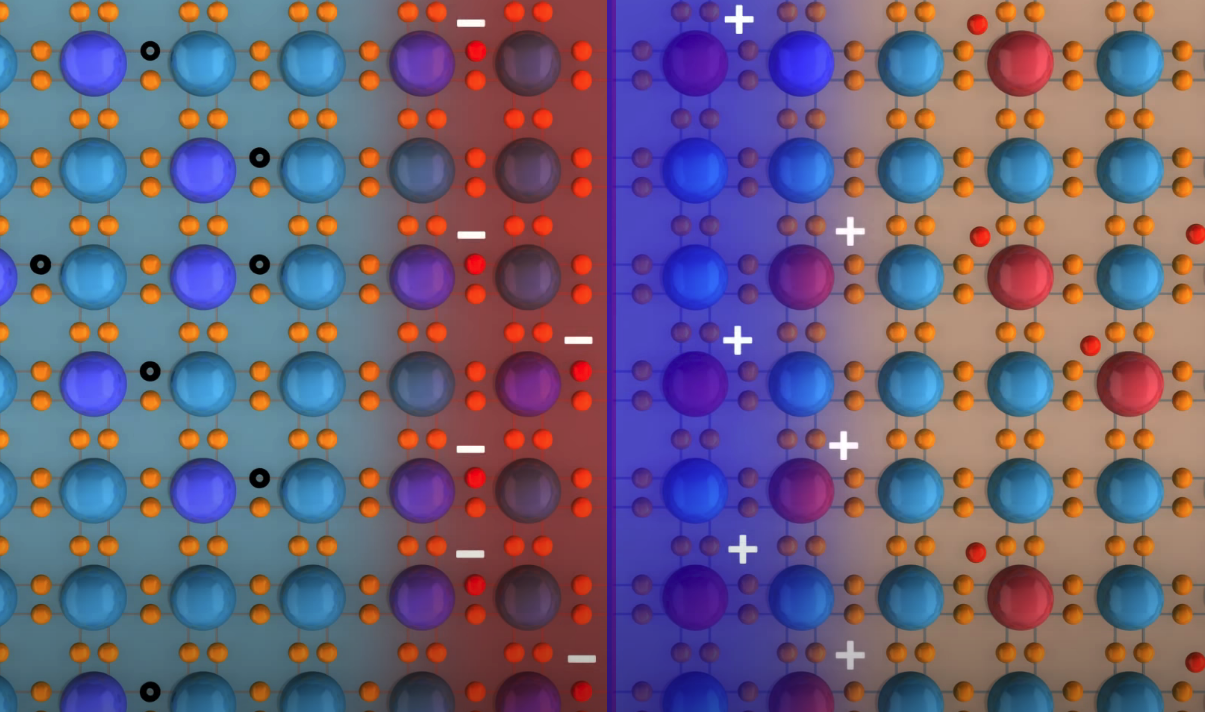

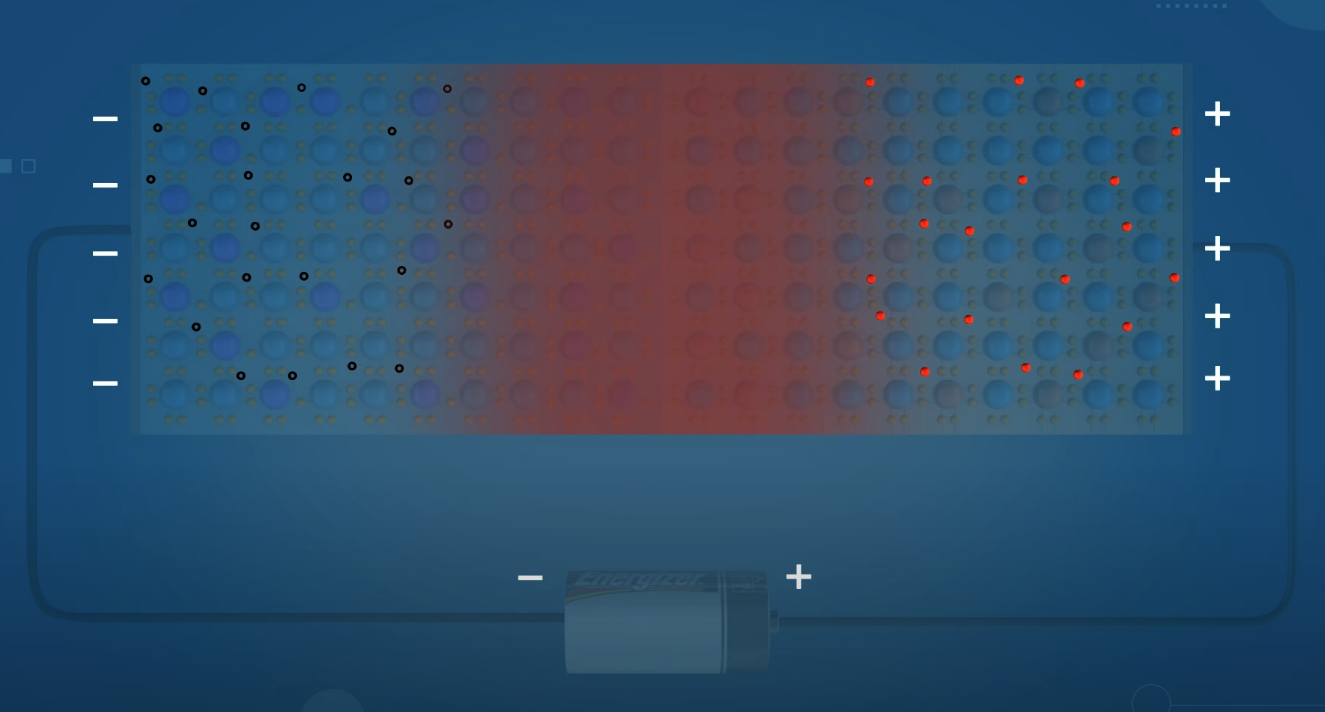

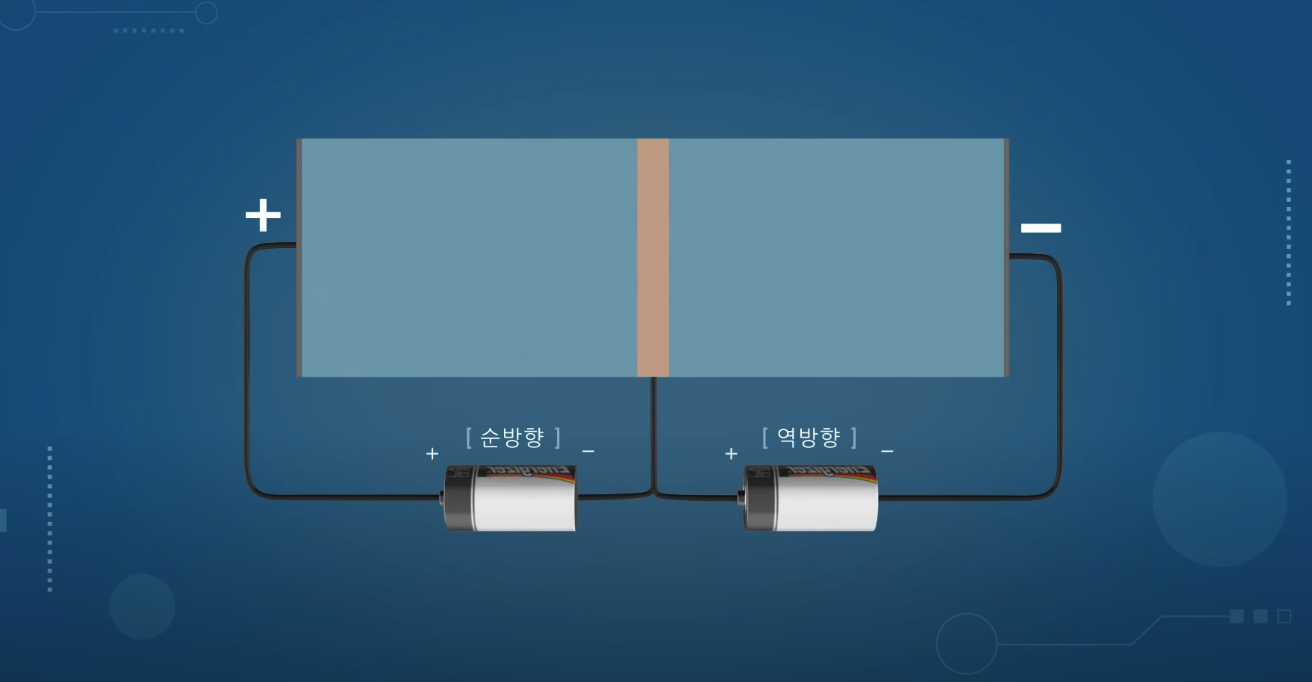

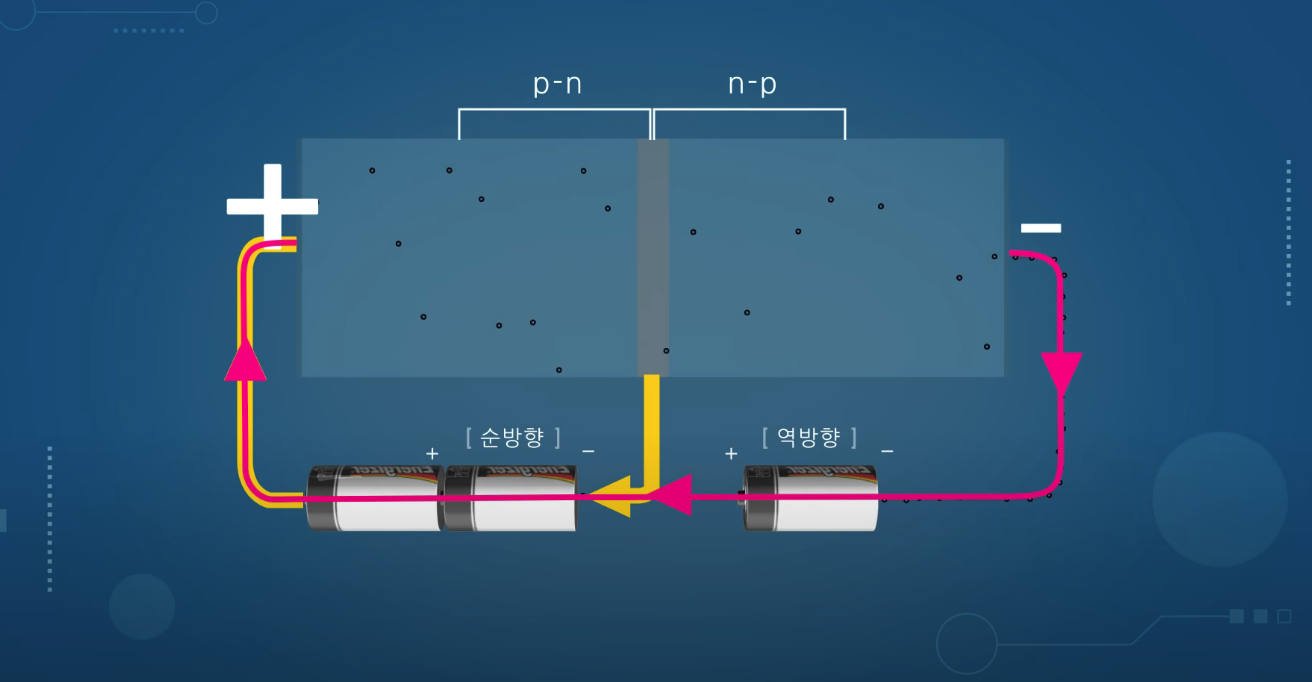

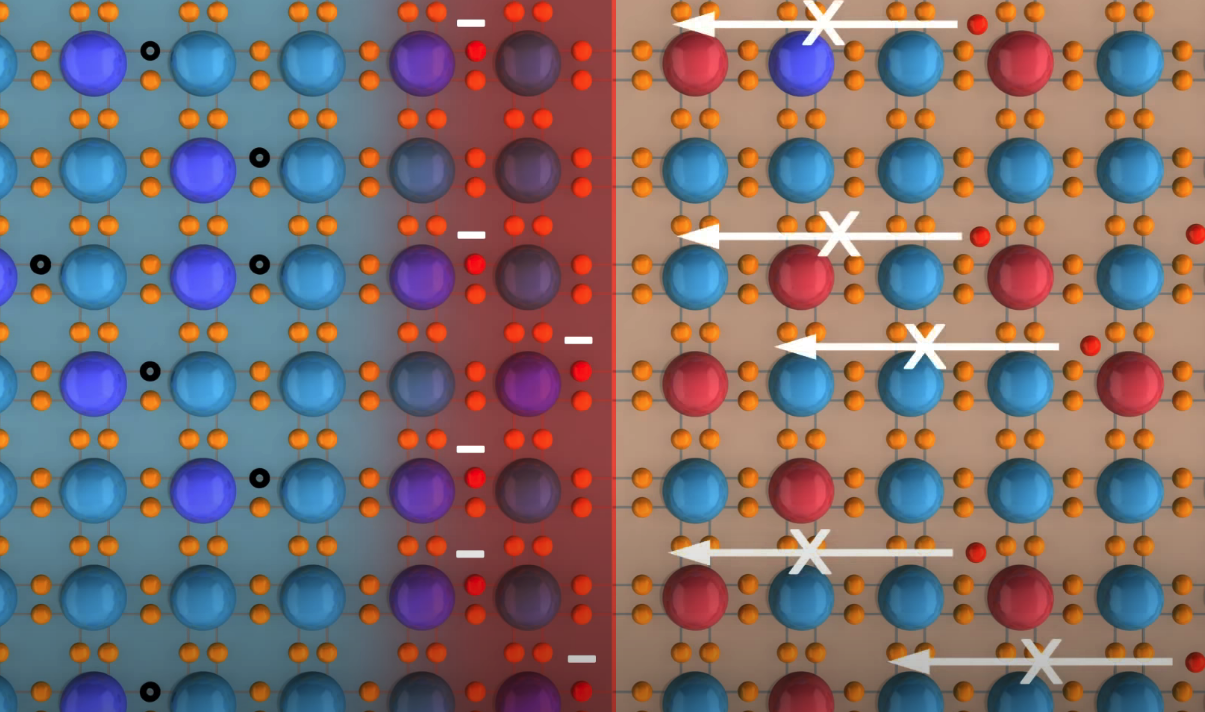

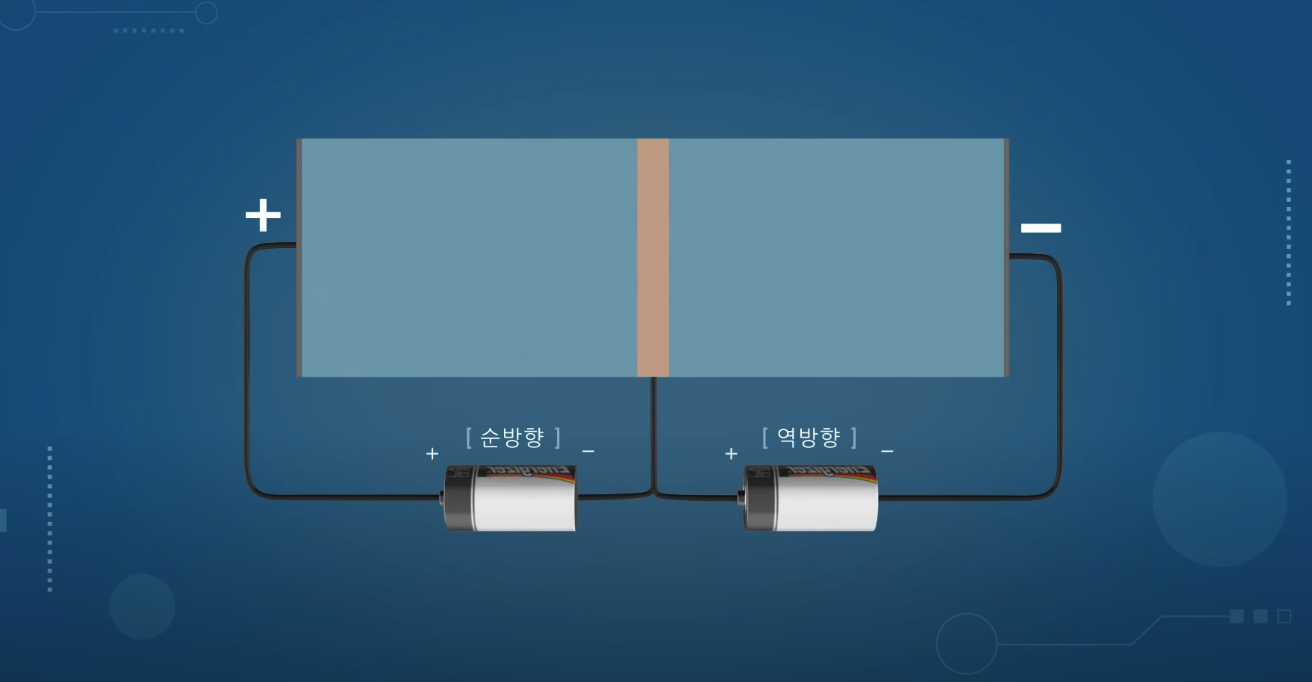

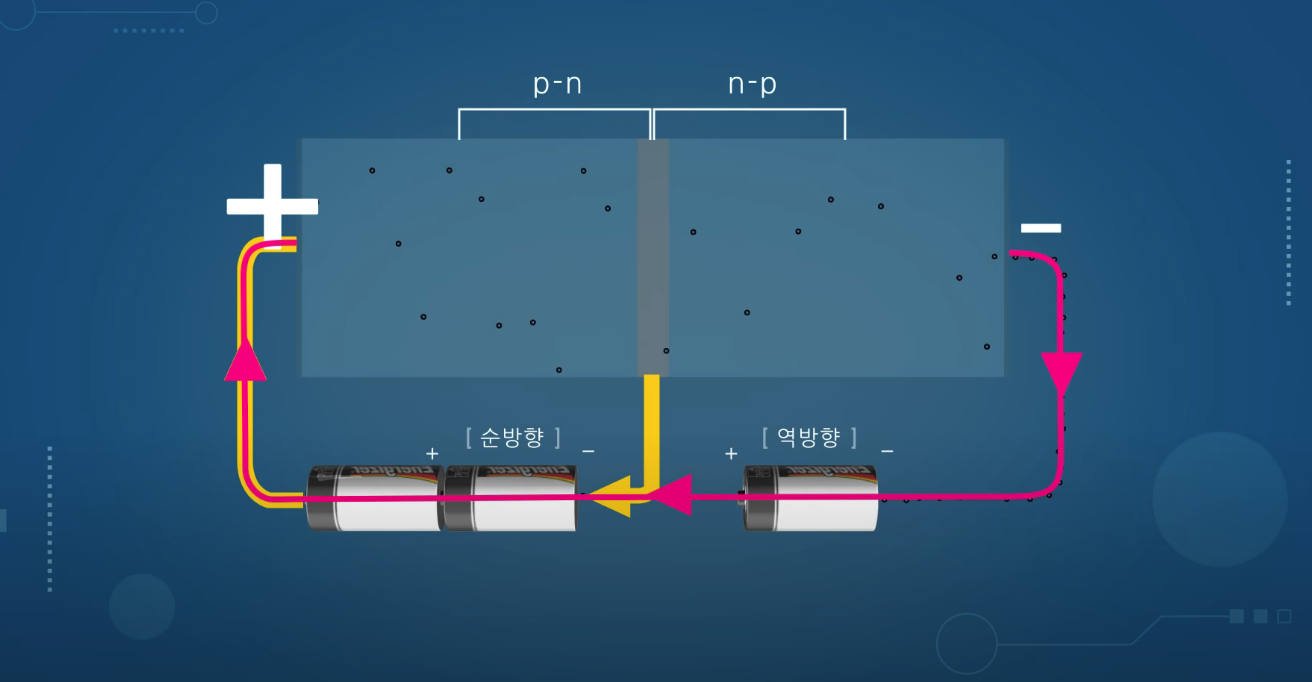

여기서 전지를 위와 같이 연결하면

P형 반도체의 양공이 -극 쪽으로(<-)

N형 반도체의 전자가 +극 쪽으로(->)

이동하게 되고, 공핍 영역이 확대되어 전하의 이동이 없어짐

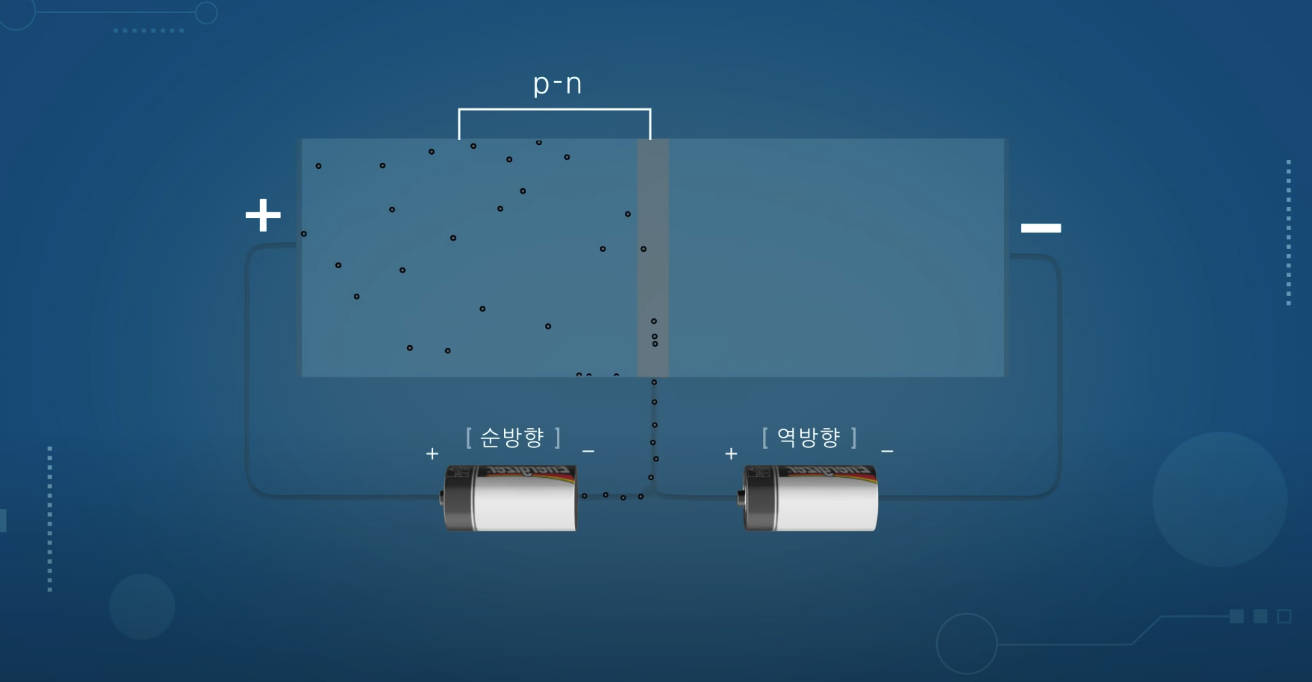

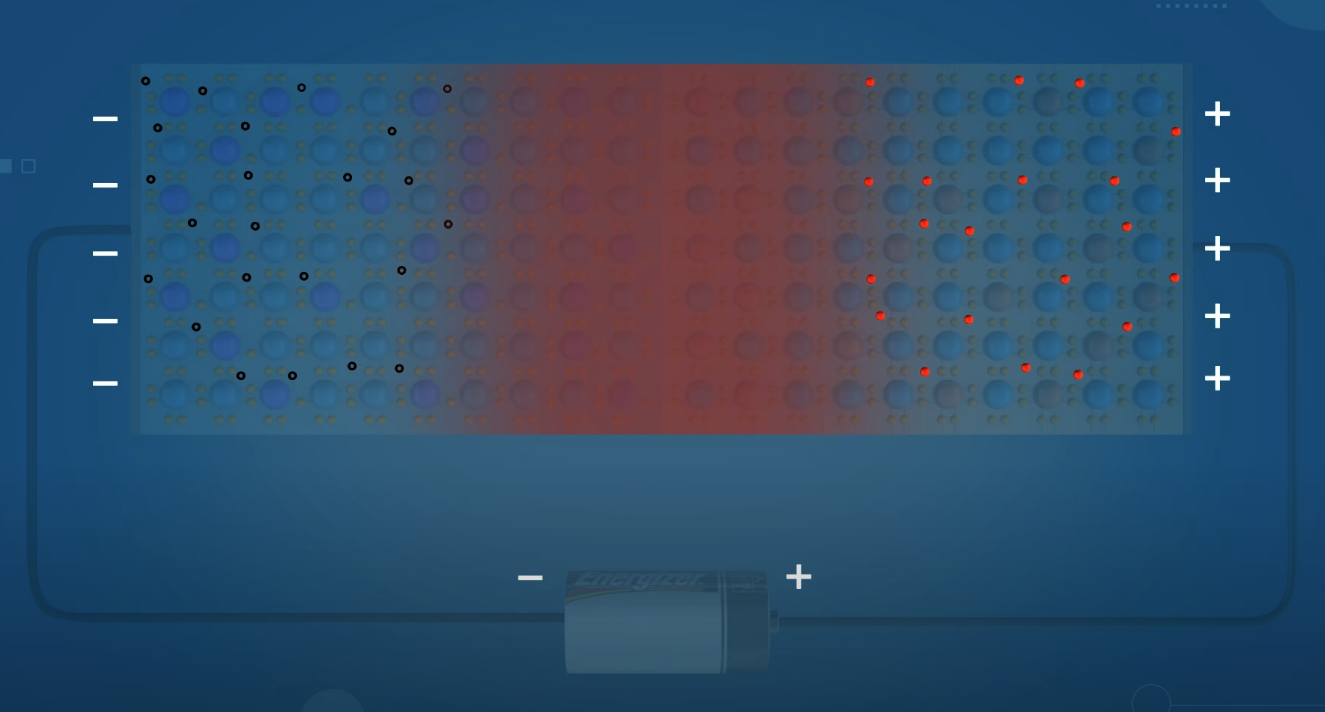

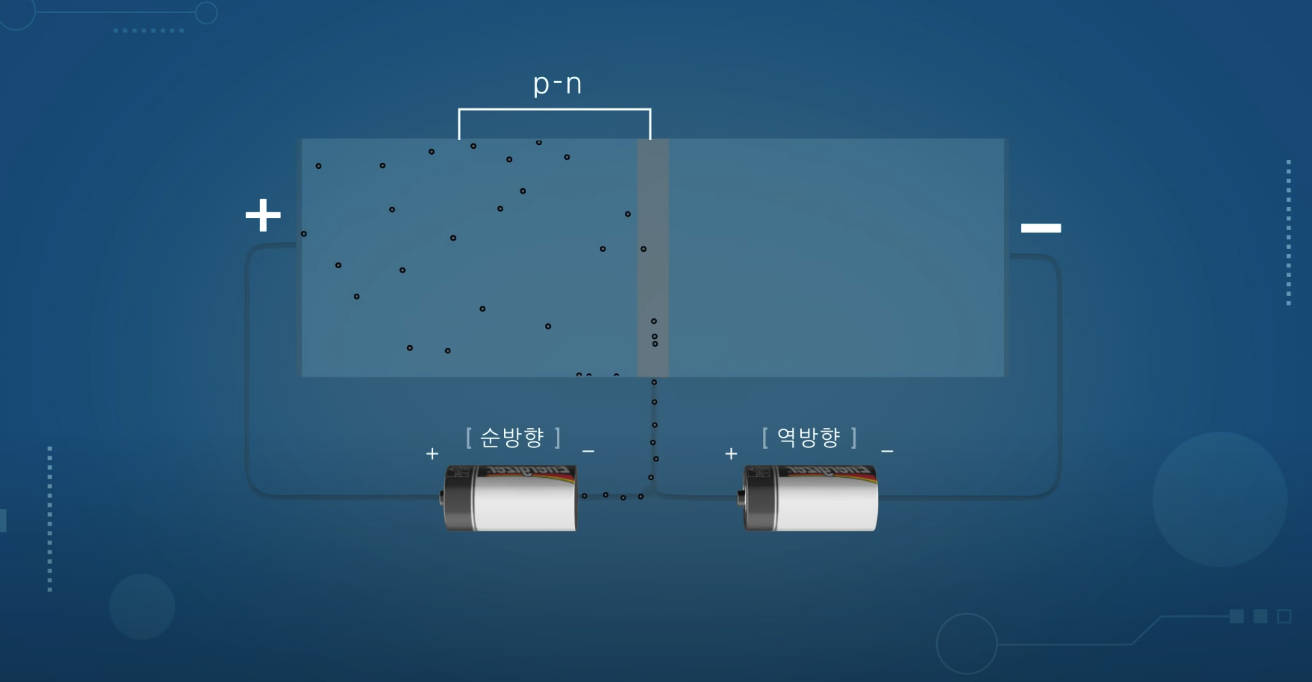

위와 같이 전지를 반대로 걸어주면

P형 반도체의 양공이 -극 쪽으로(->)

N형 반도체의 전자가 +극 쪽으로(<-)

이동하게 되고, 전류가 흐름

물론 전자가 이동하다가 중간에서 공핍 영역을 만나지만

인공적으로 걸어주는 전압이 강해 넘어갈 수 있음

즉, 전류가 흐르게 하려면 같은 전하를 가진 전압을 연결하면 됨! = 순방향 연결

전류가 흐르지 못하게 하려면 반대 전하로 전압을 연결하면됨! = 역방향 연결

P형 N형 P형을 결합하고 N형 반도체를 얇게 구성

p-n(왼쪽)에는 순방향

n-p(오른쪽)에는 역방향

방향으로 전압을 걸어줌

양공이 p-n의 순방향 부분에서만 움직이며

해당 부분에만 전류가 흐름

순방향의 전압을 키우면

n이 얇으므로

세기가 공핍 영역의 반발력을 이겨

n-p 영역까지 넘어가는 양공이 생김

순방향의 전압이 세지면서 p-n-p 영역을 이르러 전류가 흐르게 됨

역방향의 전압을 키우면 흐르는 전류의 양이 더 많아지게 됨

즉, 전압의 일정 세기에 따라

반도체에 전류가 흐르게 할 수도, 흐르지 않게 할 수도 있음

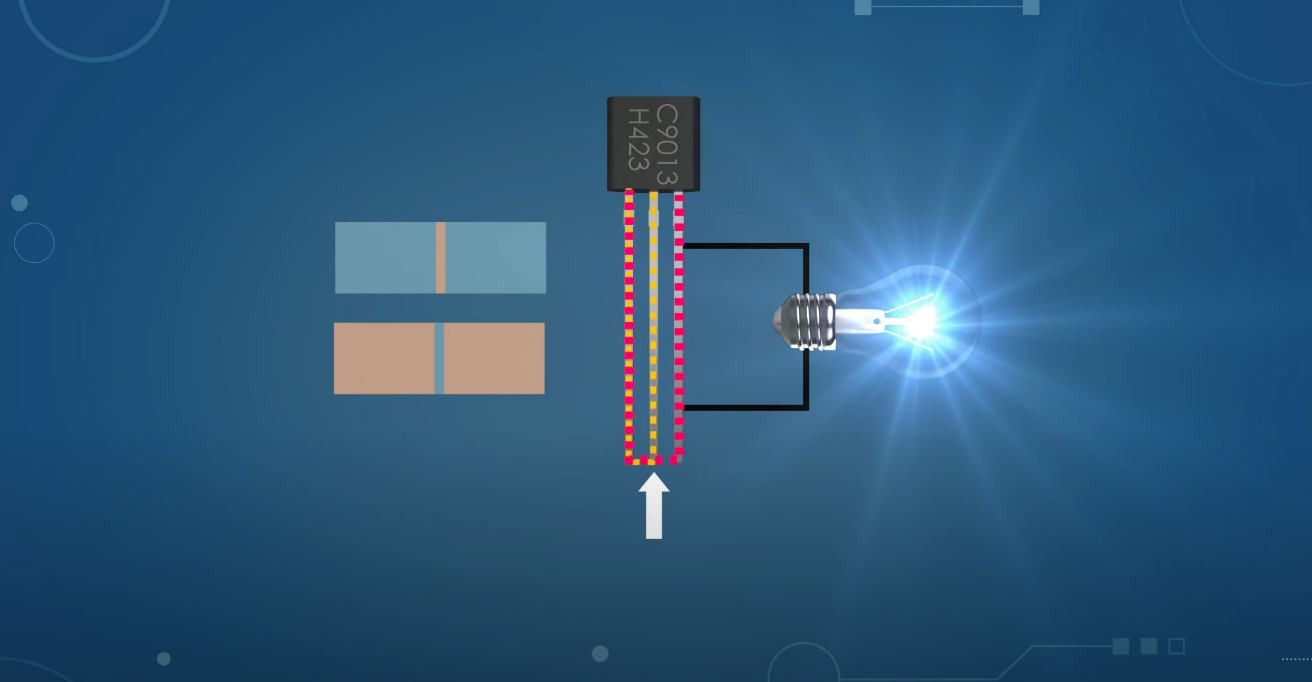

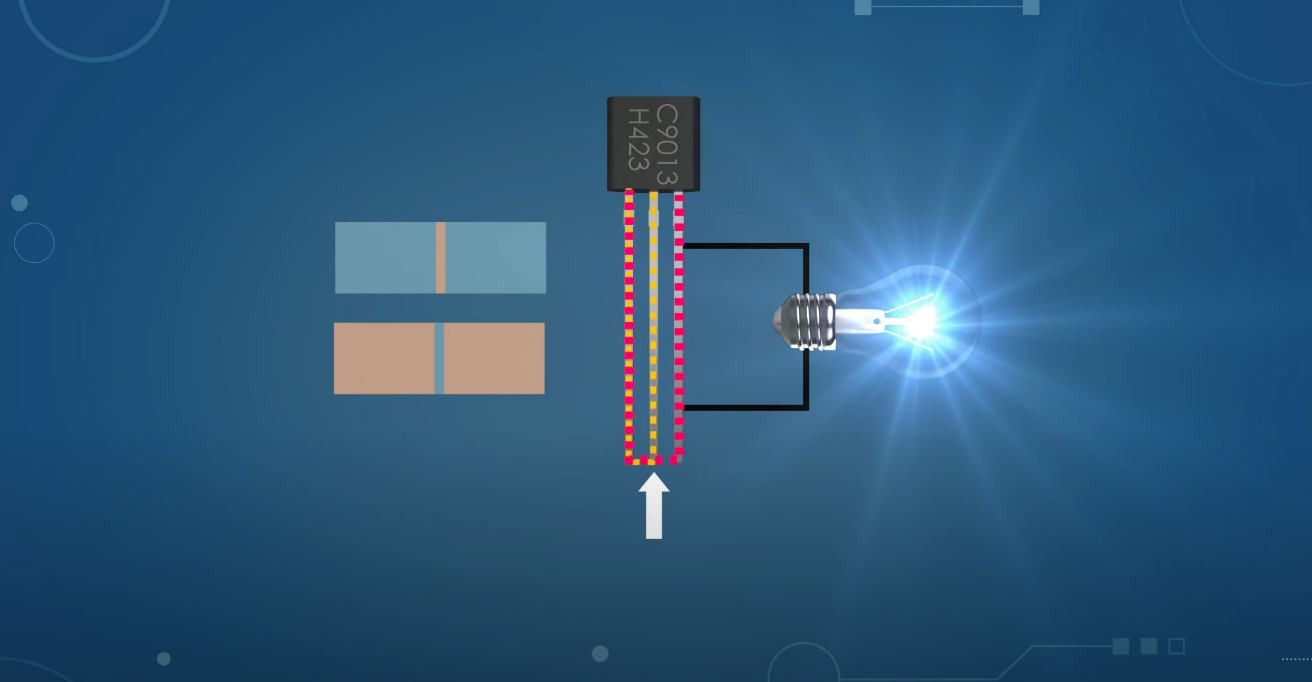

해당 방식으로 스위치 작용을 해주는 반도체를 트랜지스터라고 함

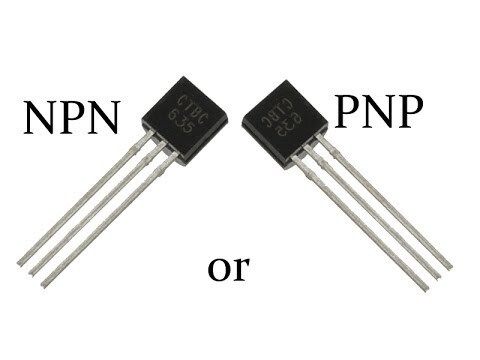

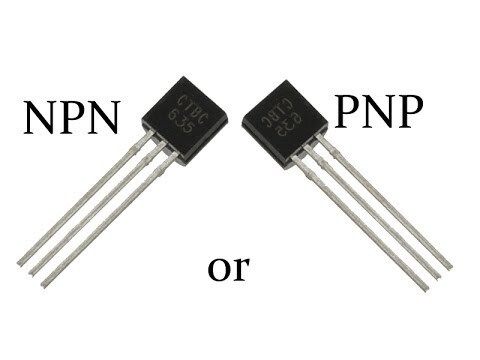

트랜지스터는 일반적으로 이렇게 생겼으며

PNP, NPN 종류가 있음

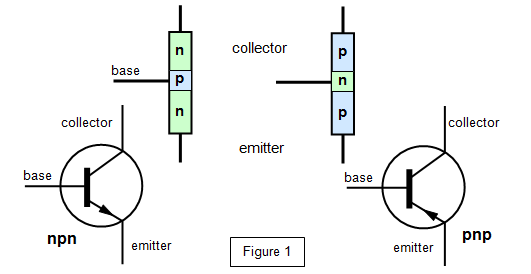

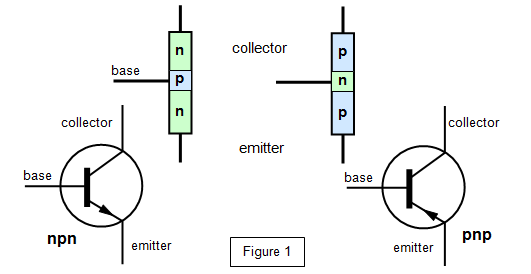

트랜지스터는 Emitter(E), Collector(C), Base(B)로 구성

위에서 봤듯이 Base에 전류가 흐르면

NPN : C -> E로 전류가 흐름

PNP : E -> C로 전류가 흐름

즉, 가운데 도선(B)에 특정 전압을 걸어주면

전류가 흐름

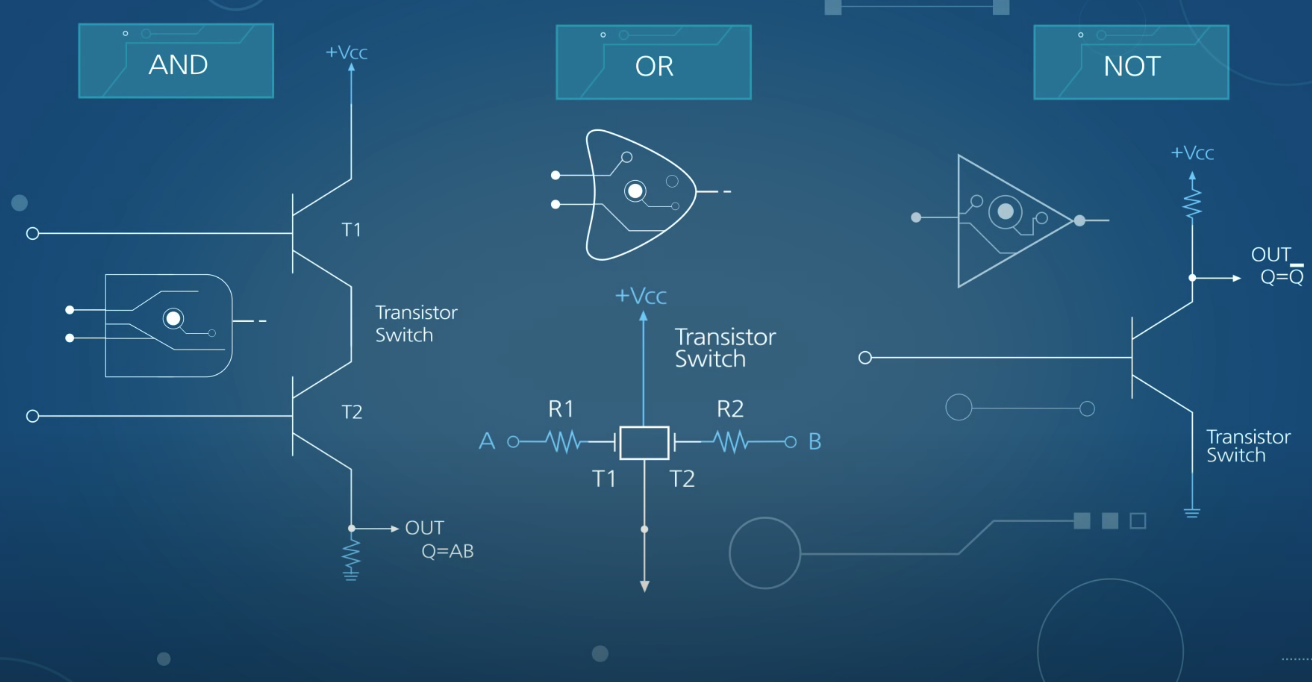

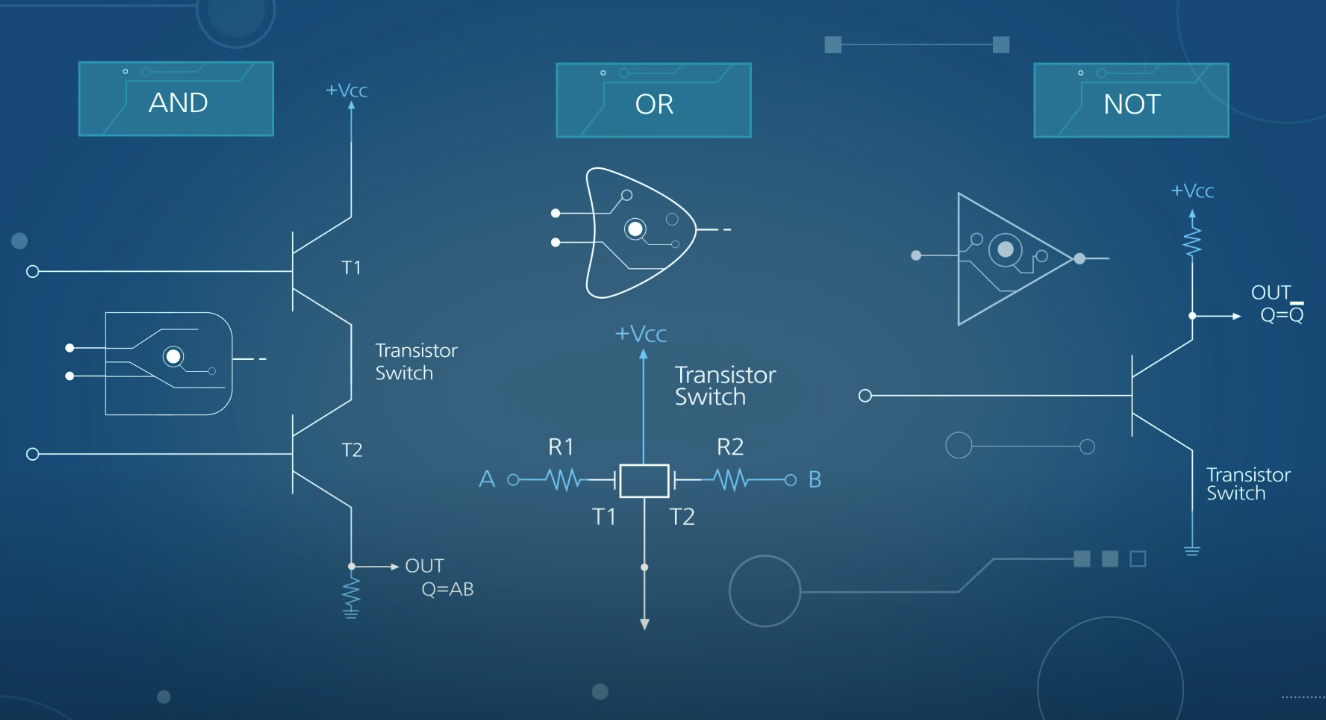

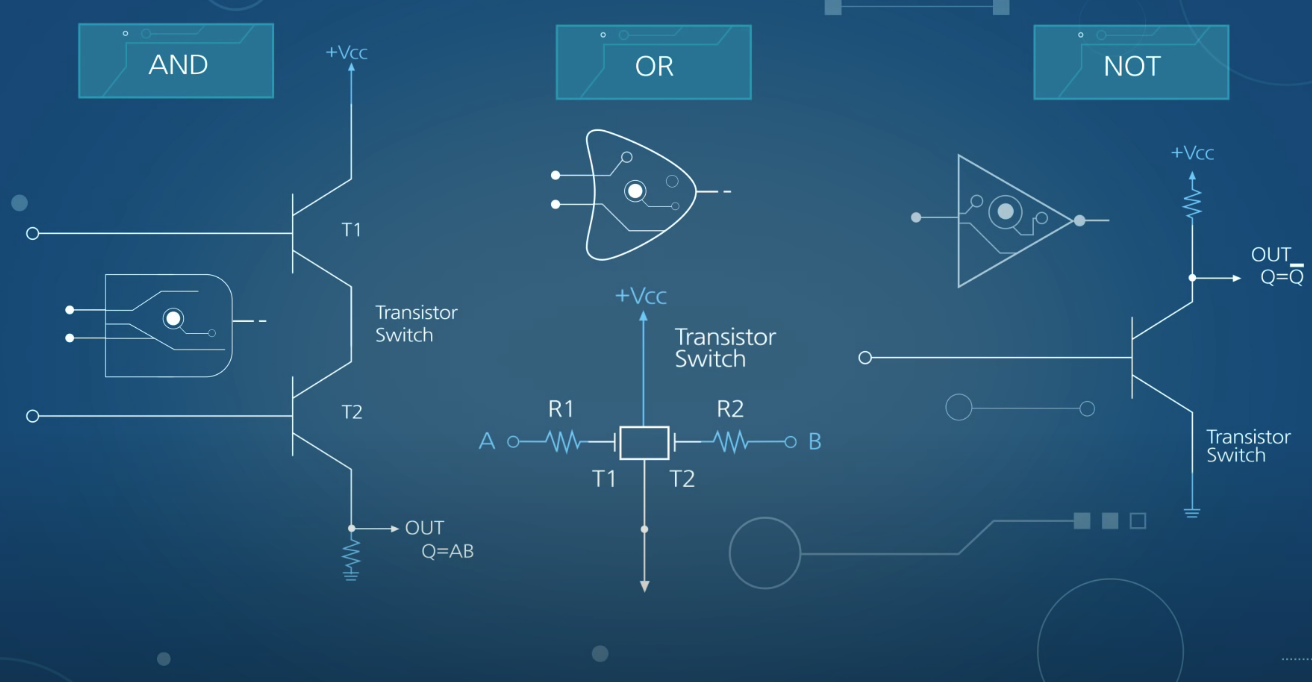

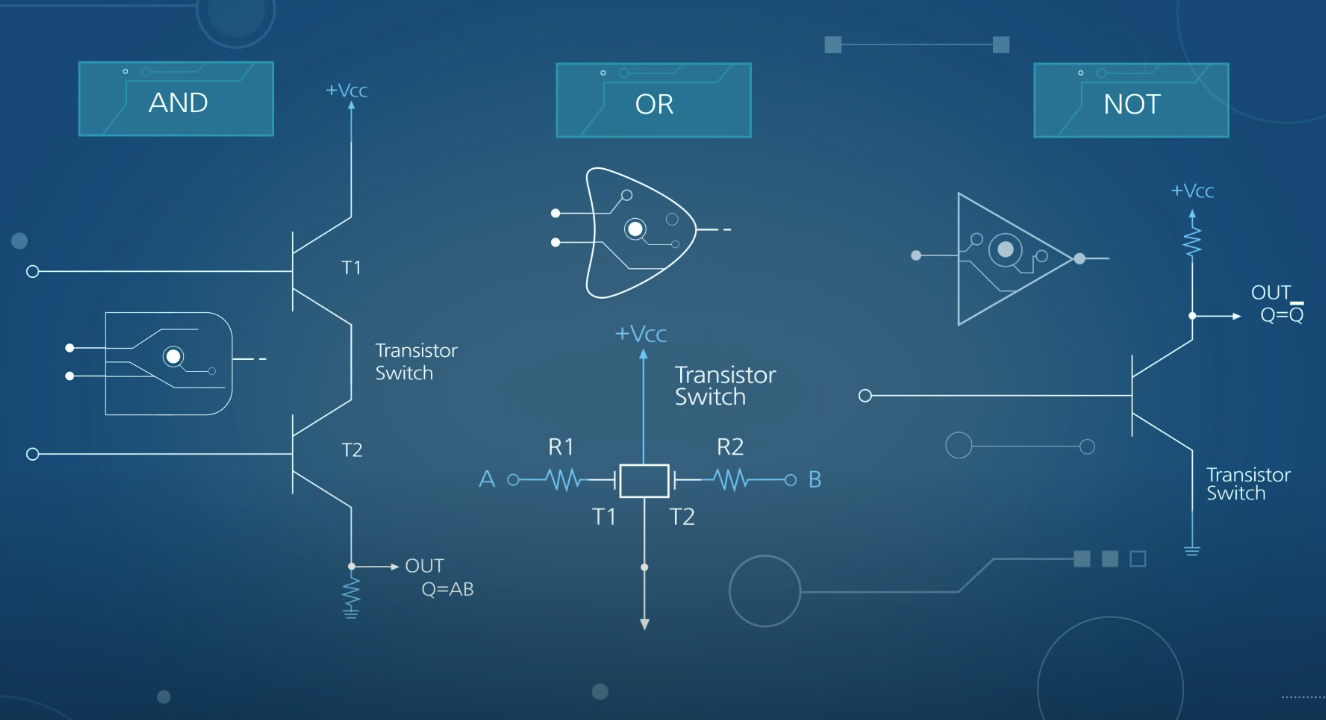

이 트랜지스터를 이용하면

우리가 배운 논리회로를 구현할 수 있음

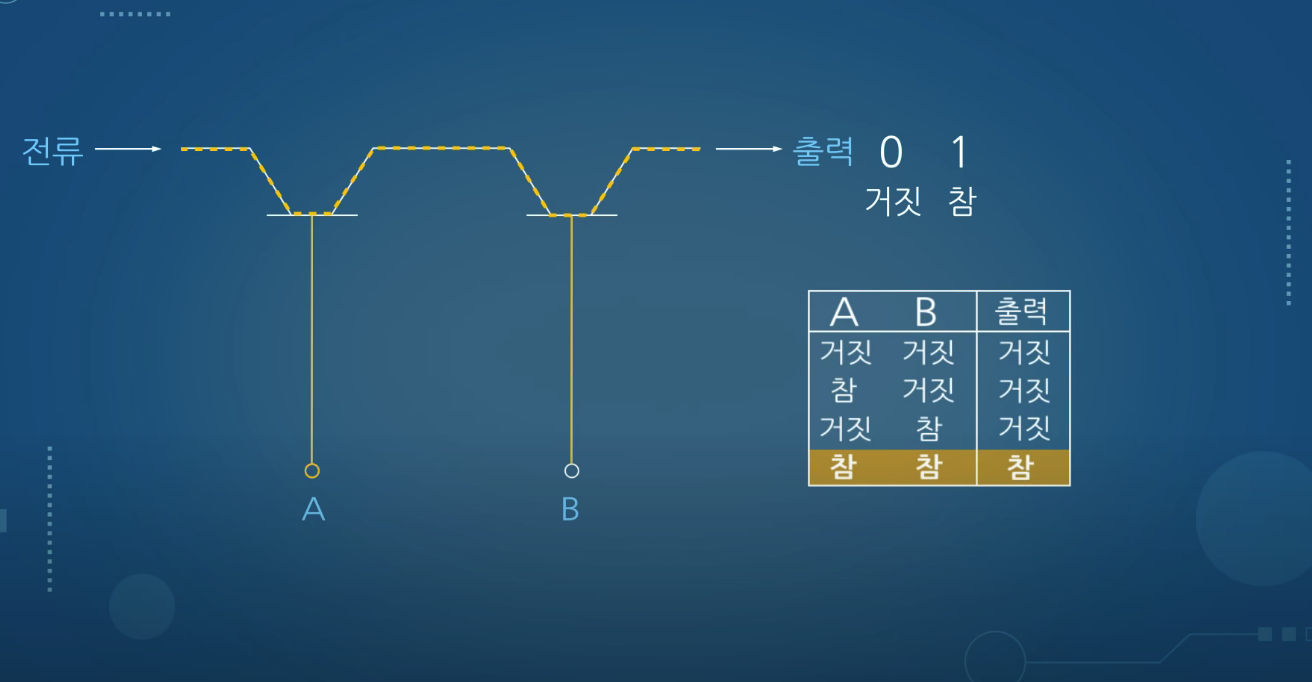

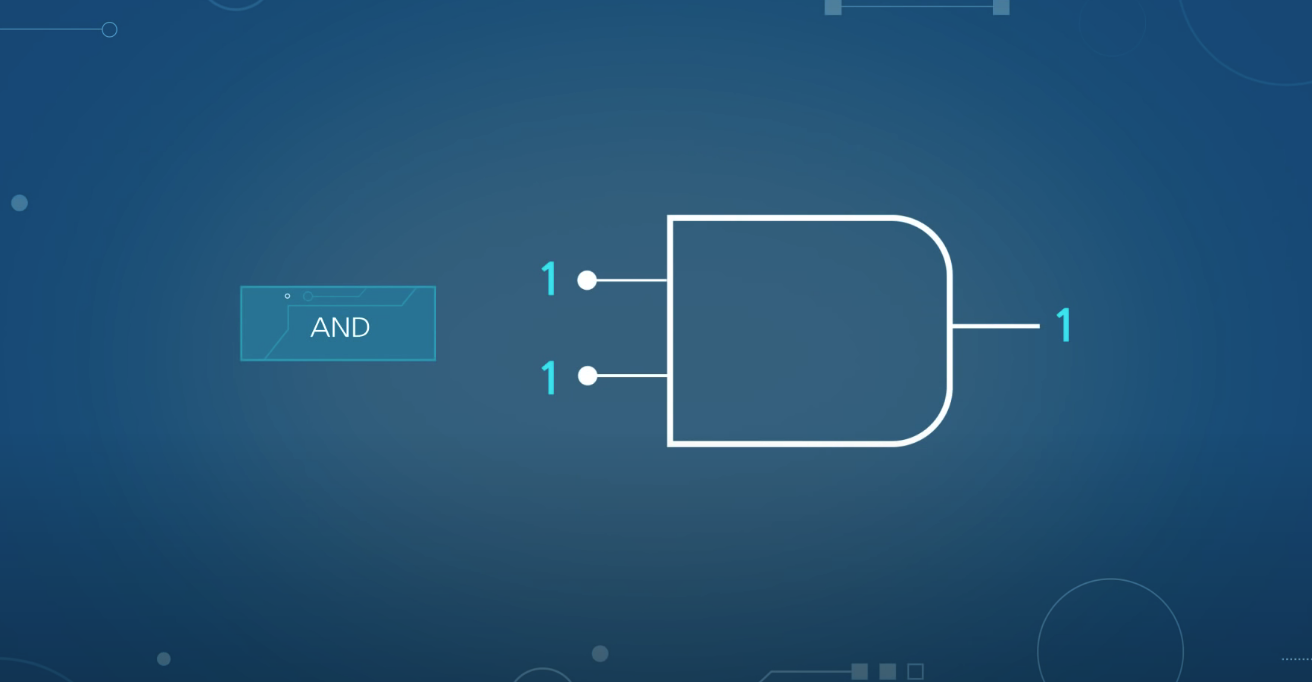

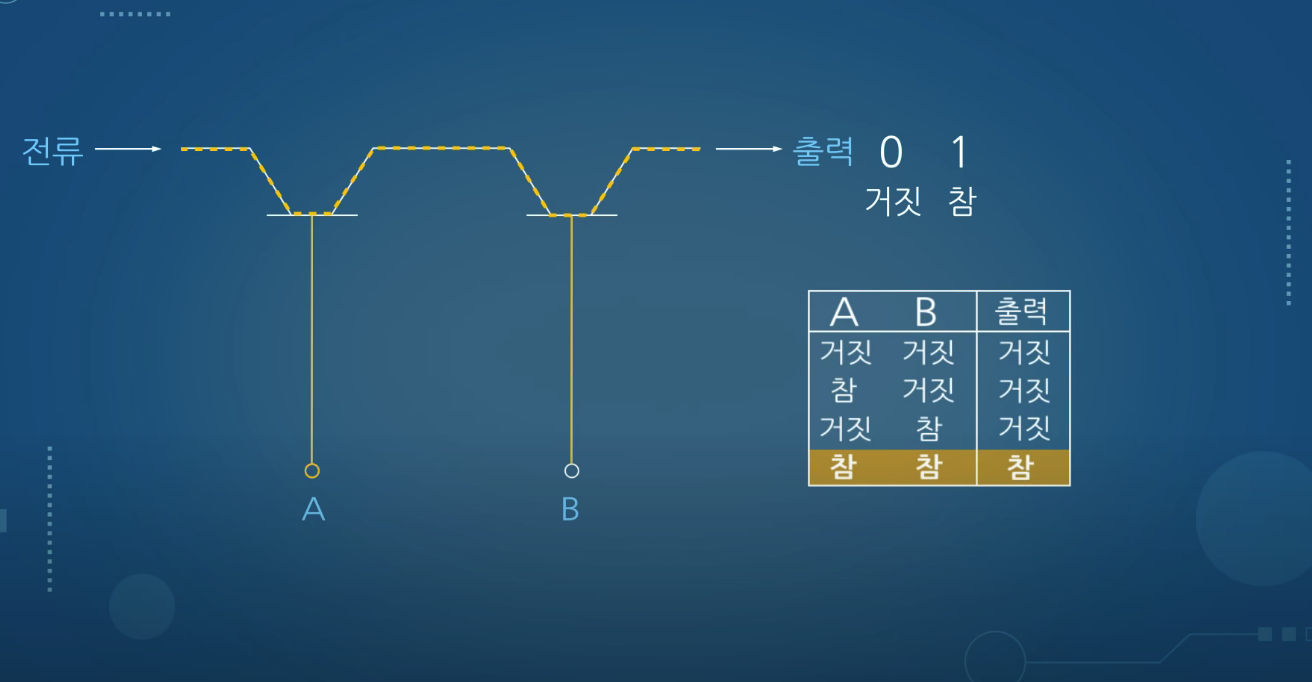

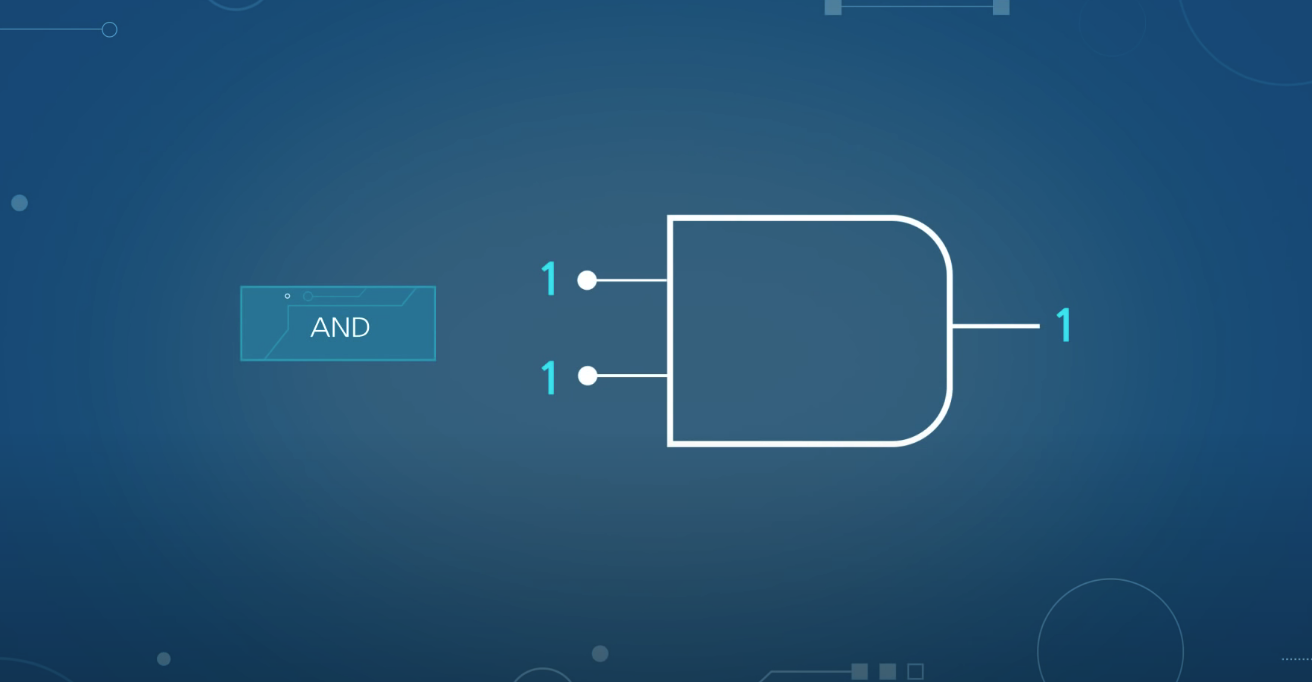

트랜지스터 두 개를 직렬로 연결해

각 Base 부분인 A, B에 전류의 여부에 따라

출력이 결정되며

이는 우리가 알고 있는 AND 게이트가 된다

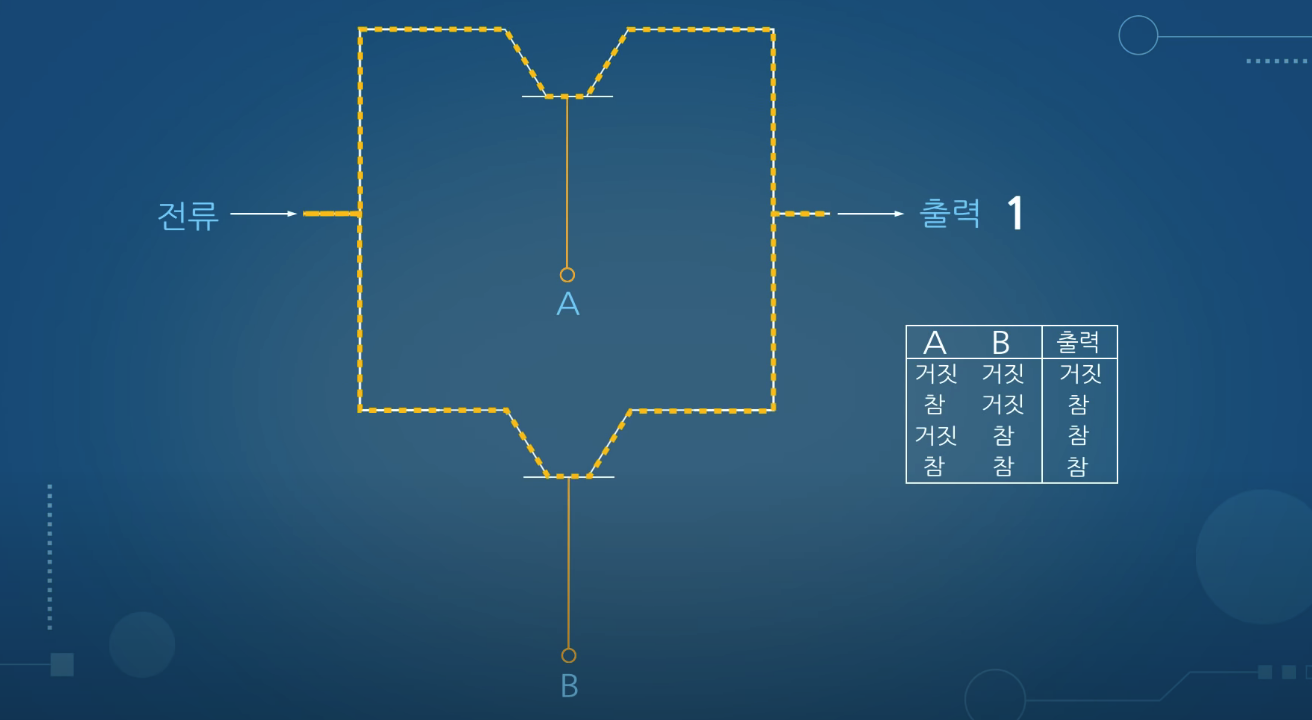

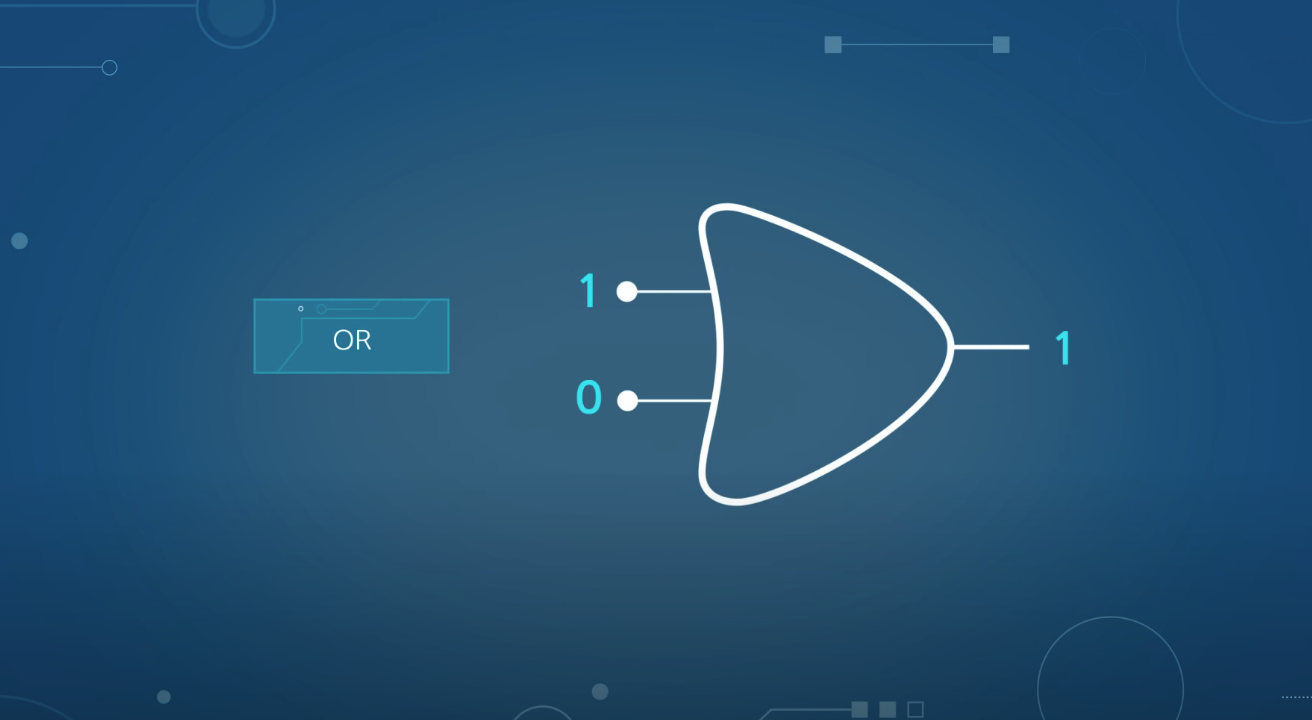

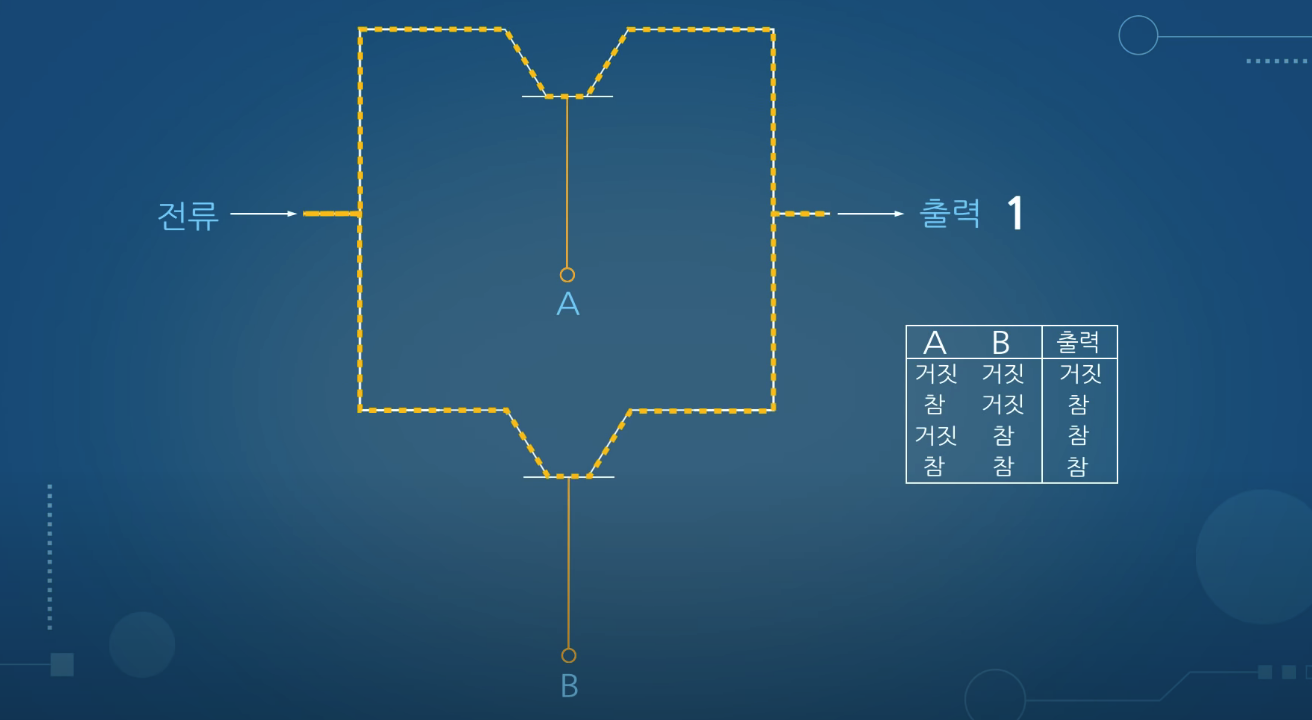

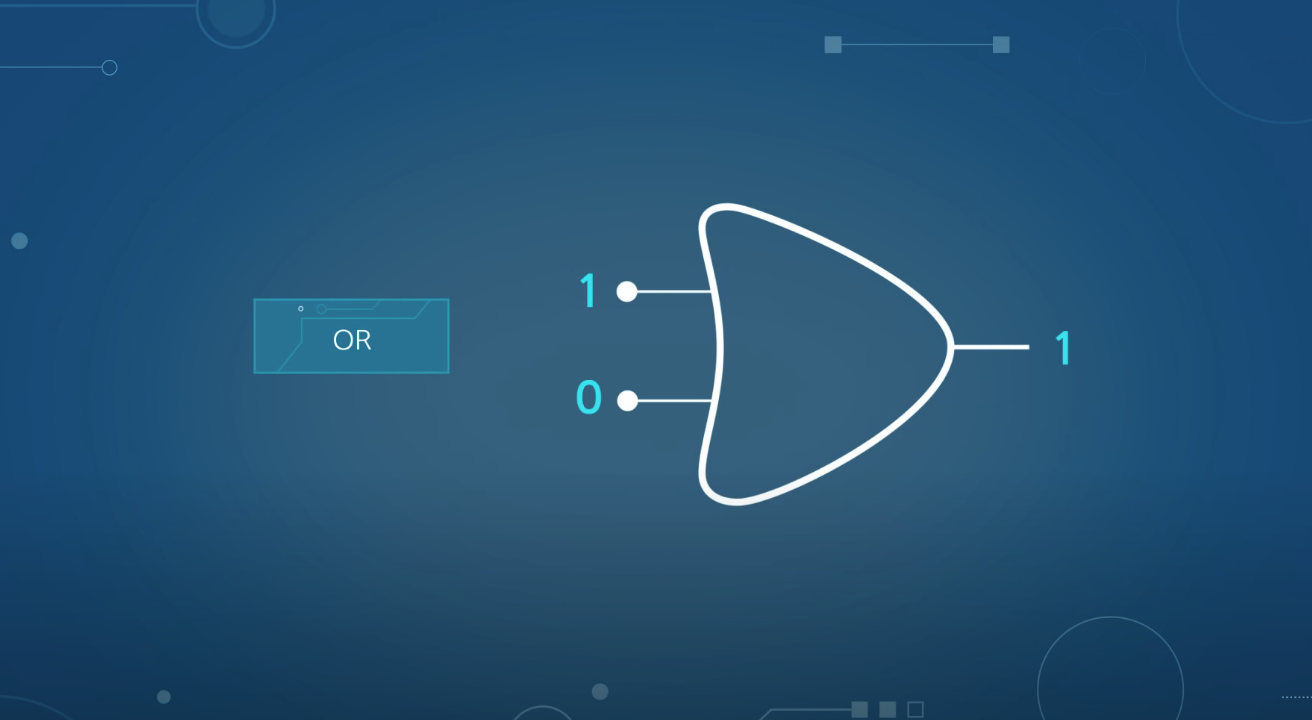

트랜지스터를 병렬로 연결하면

우리가 알고 있는 OR 게이트이다

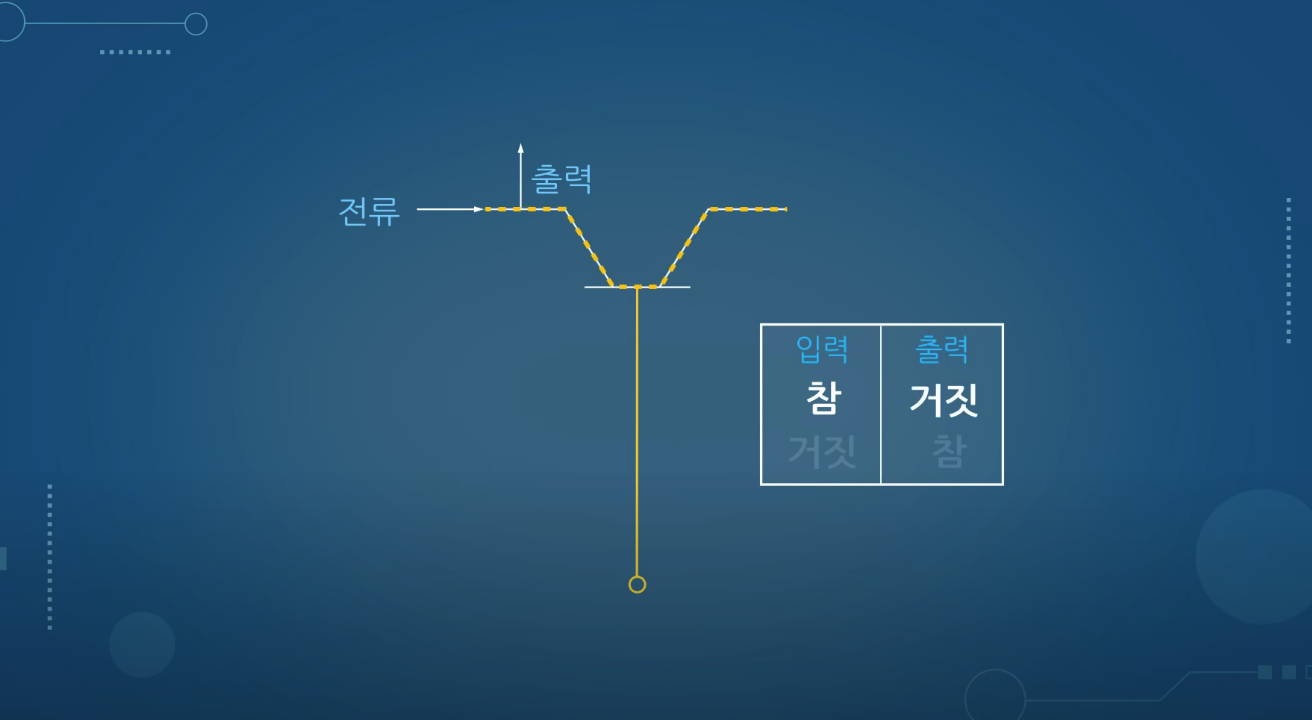

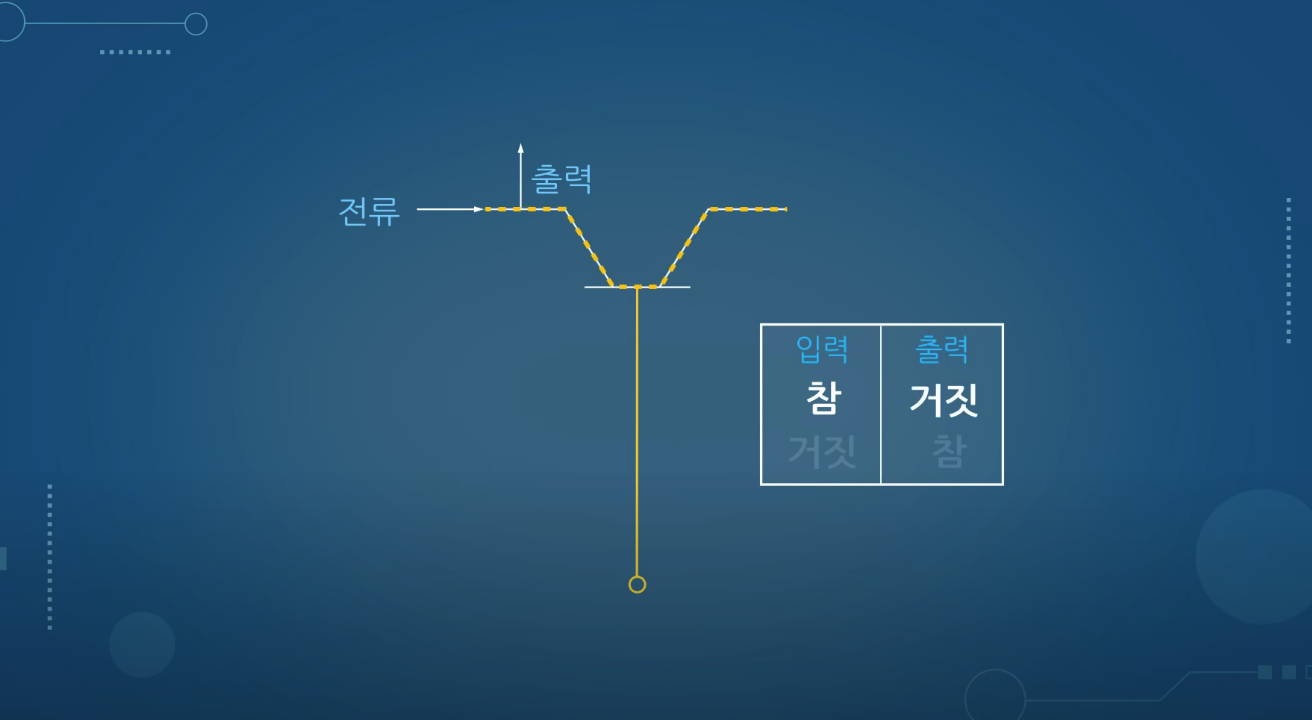

NOT 게이트는 출력을 트랜지스터 앞에 달면

Base에 전류가 없는 경우

출력으로 전류가 흐르고

Base에 전류를 흘려주면

트랜지스터 쪽으로 전류가 흐르게 됨

NOT 게이트

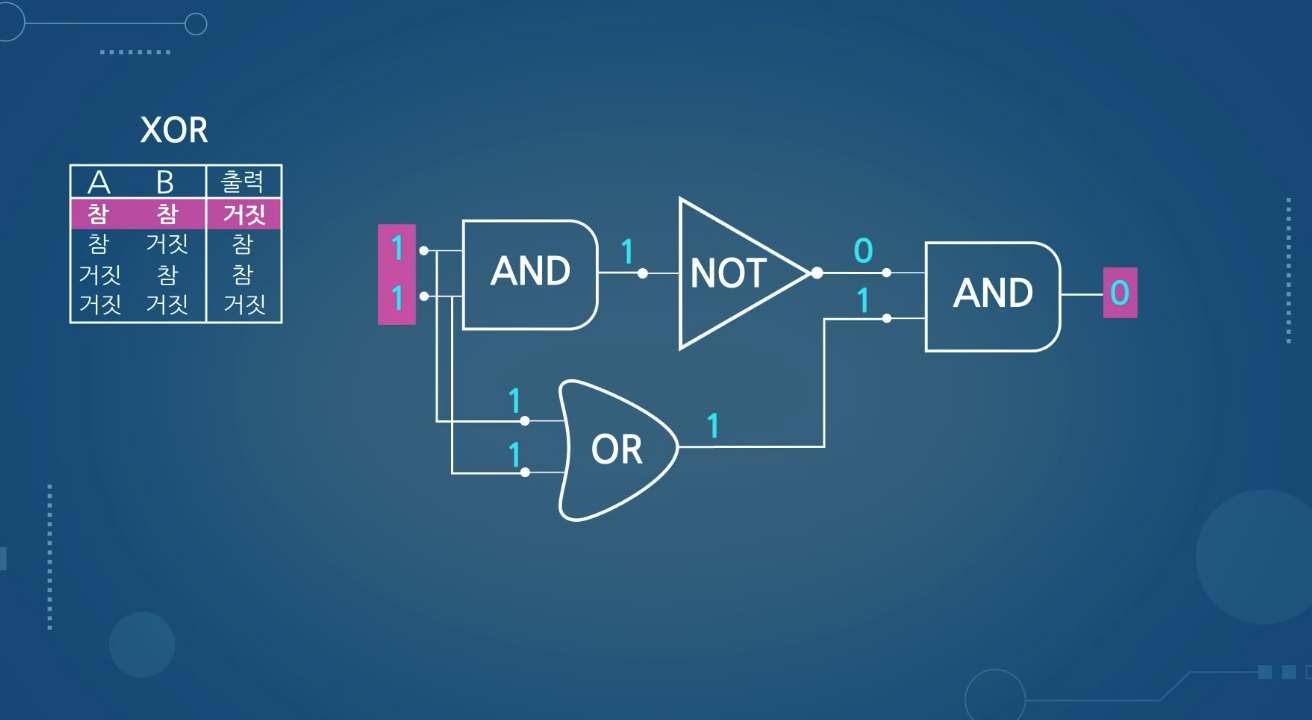

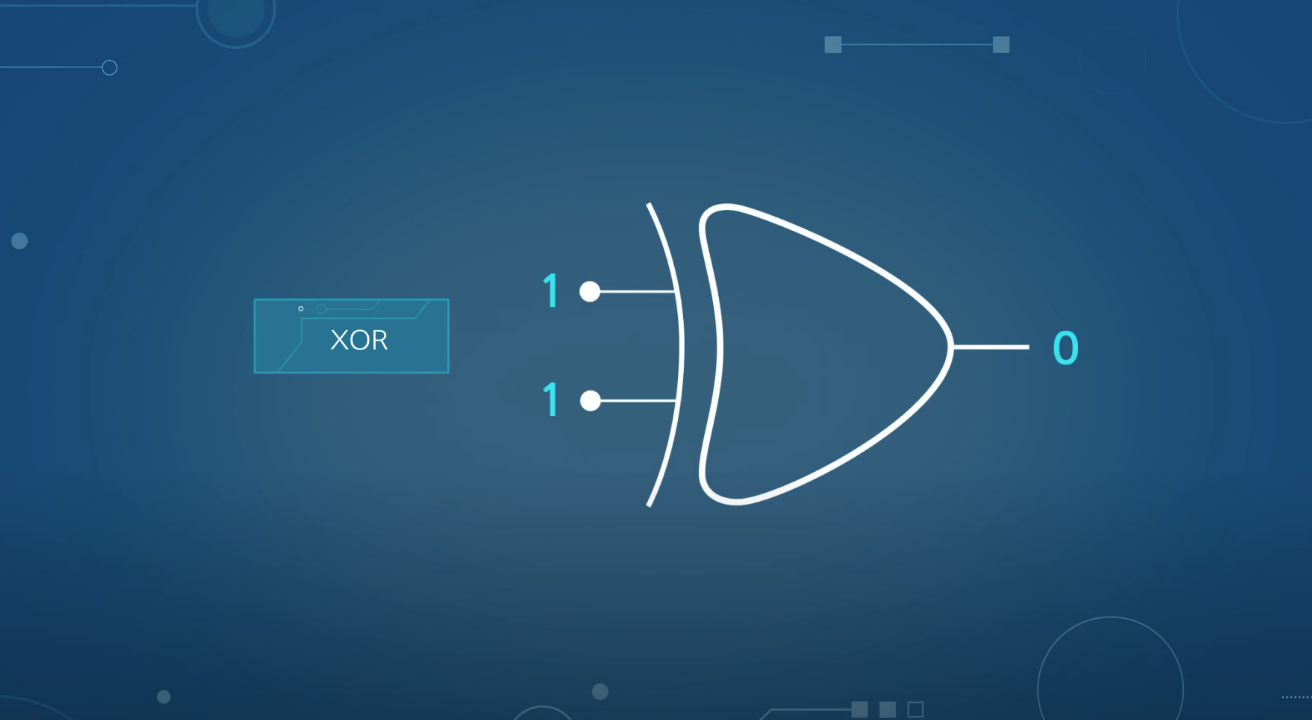

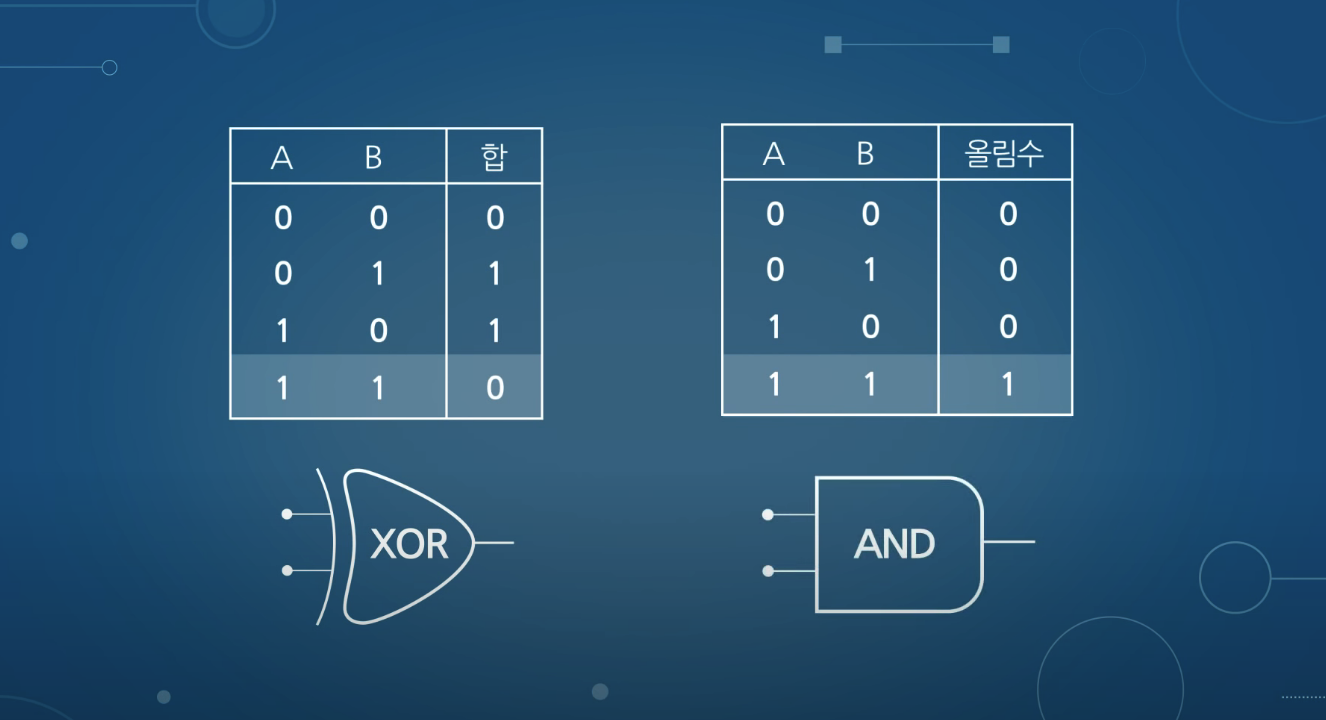

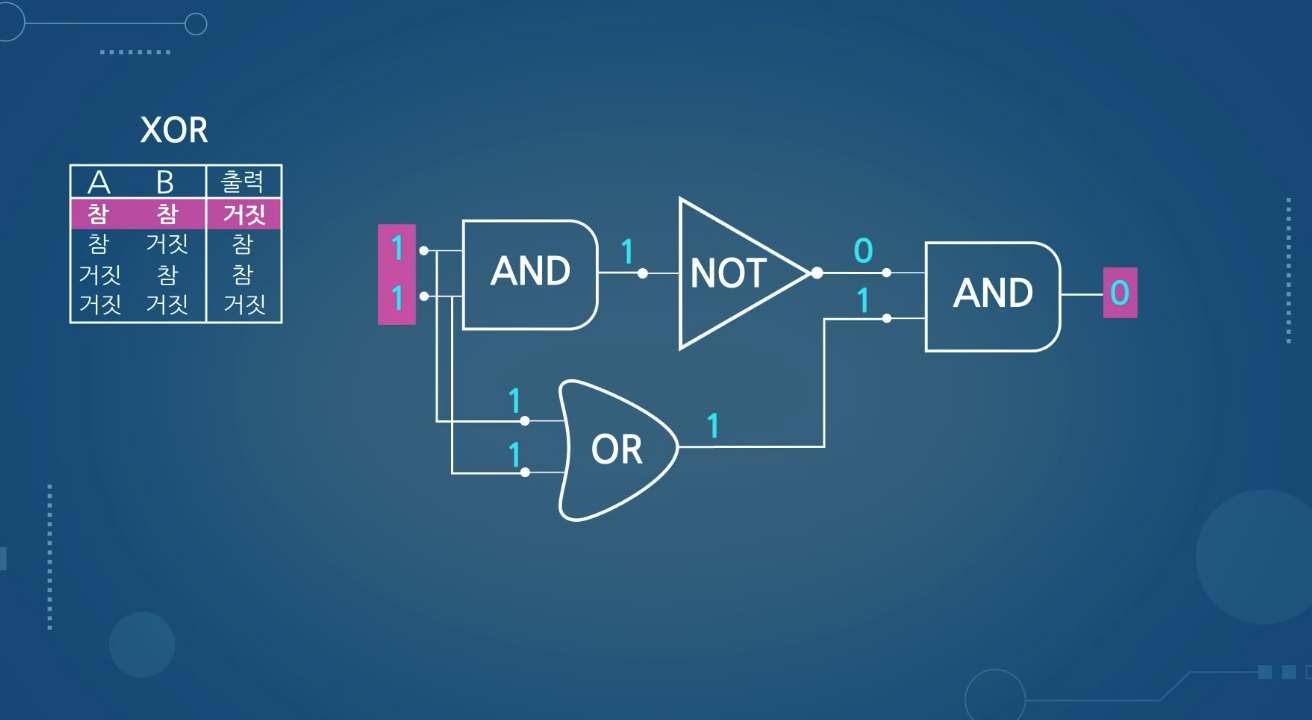

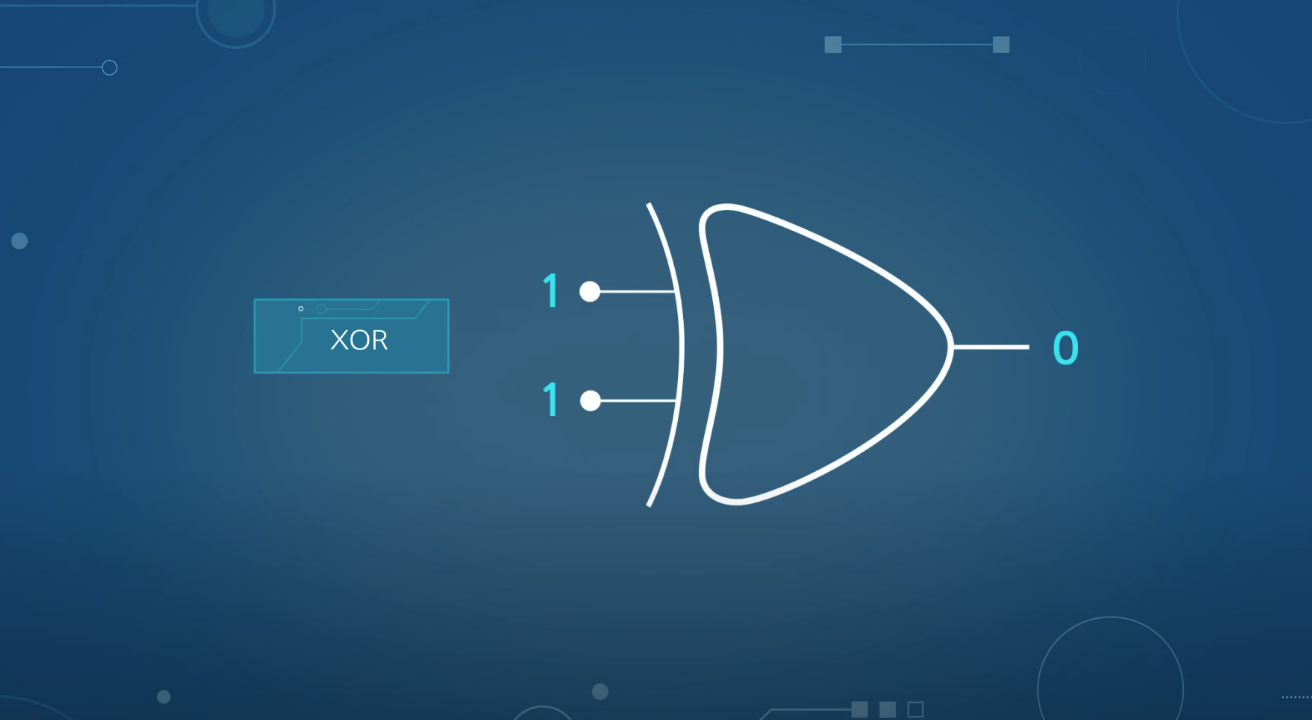

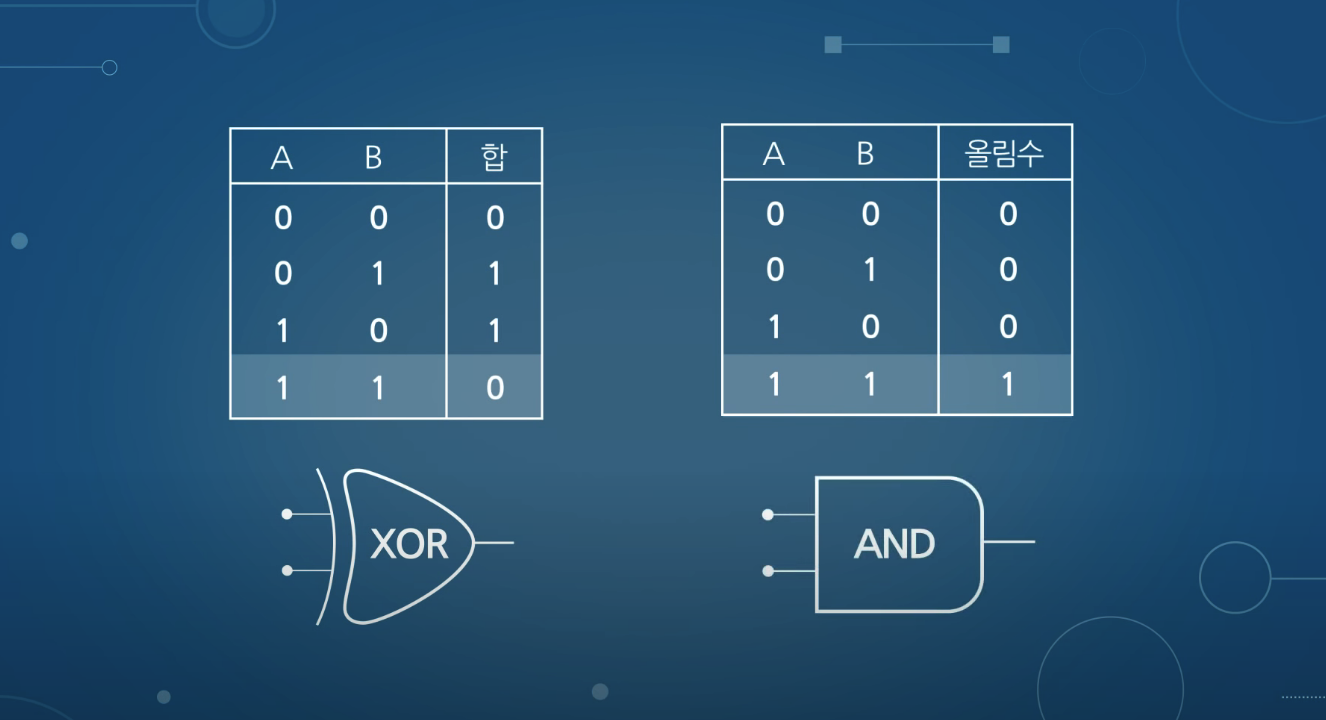

위에서 나온 게이트들을 조합하여 XOR 게이트 구성 가능

XOR 게이트

AND / OR / NOT 회로 도식화

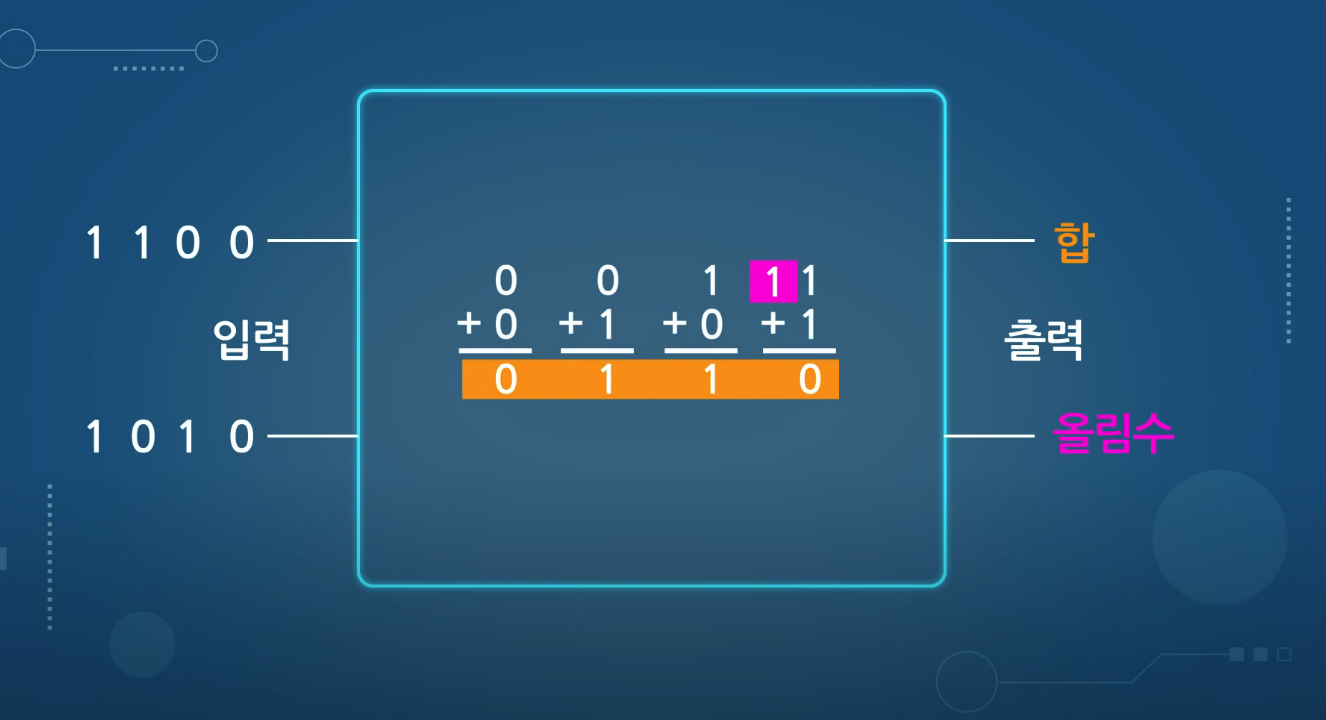

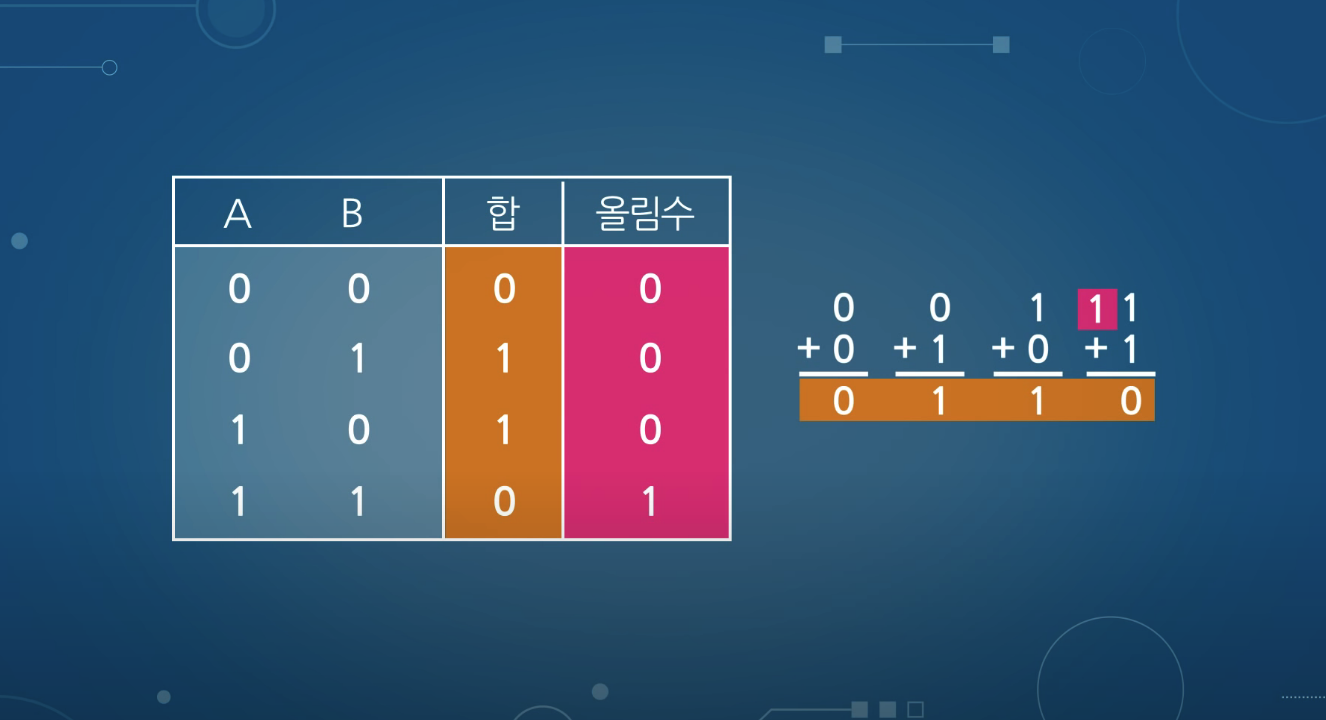

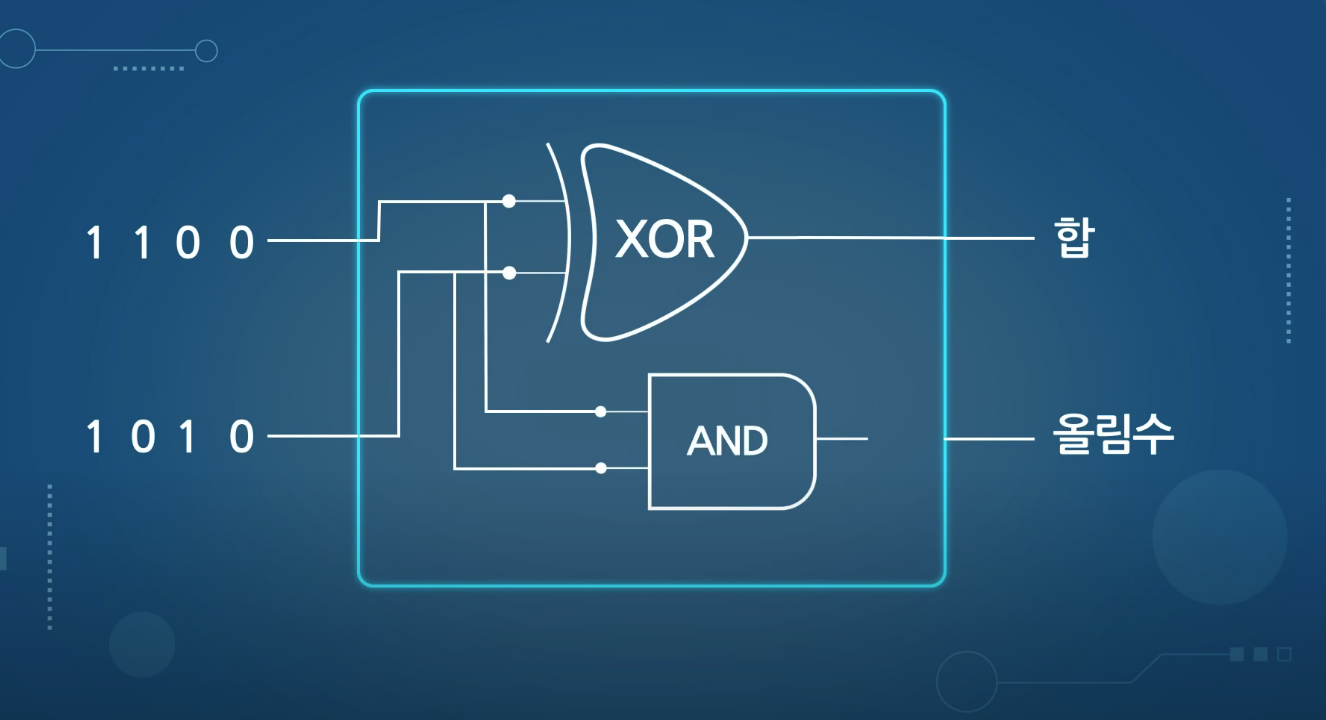

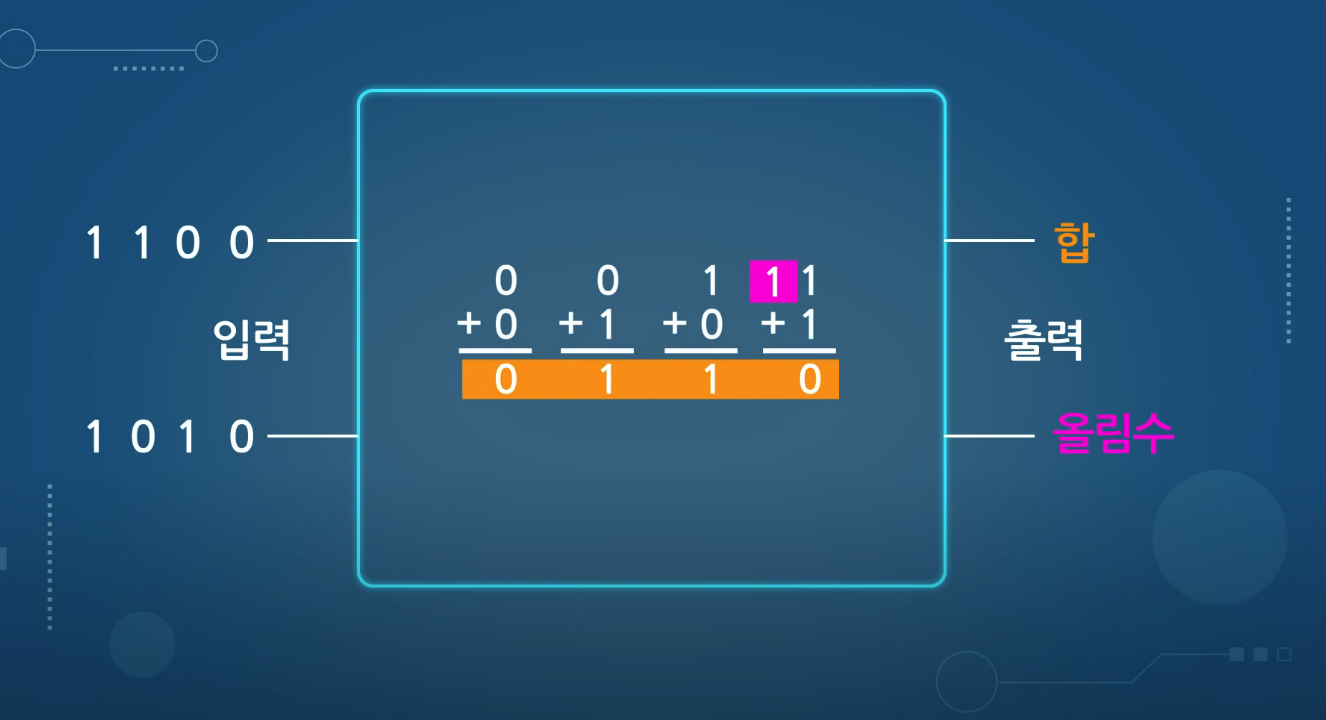

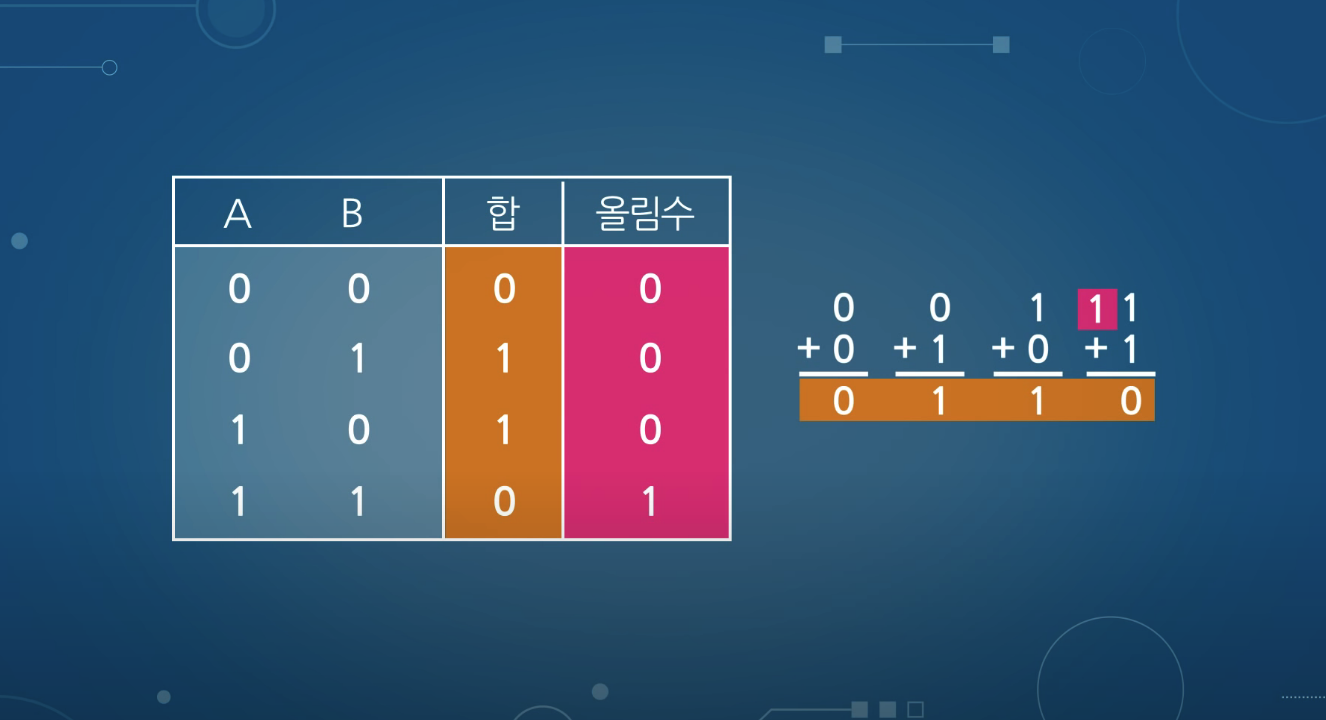

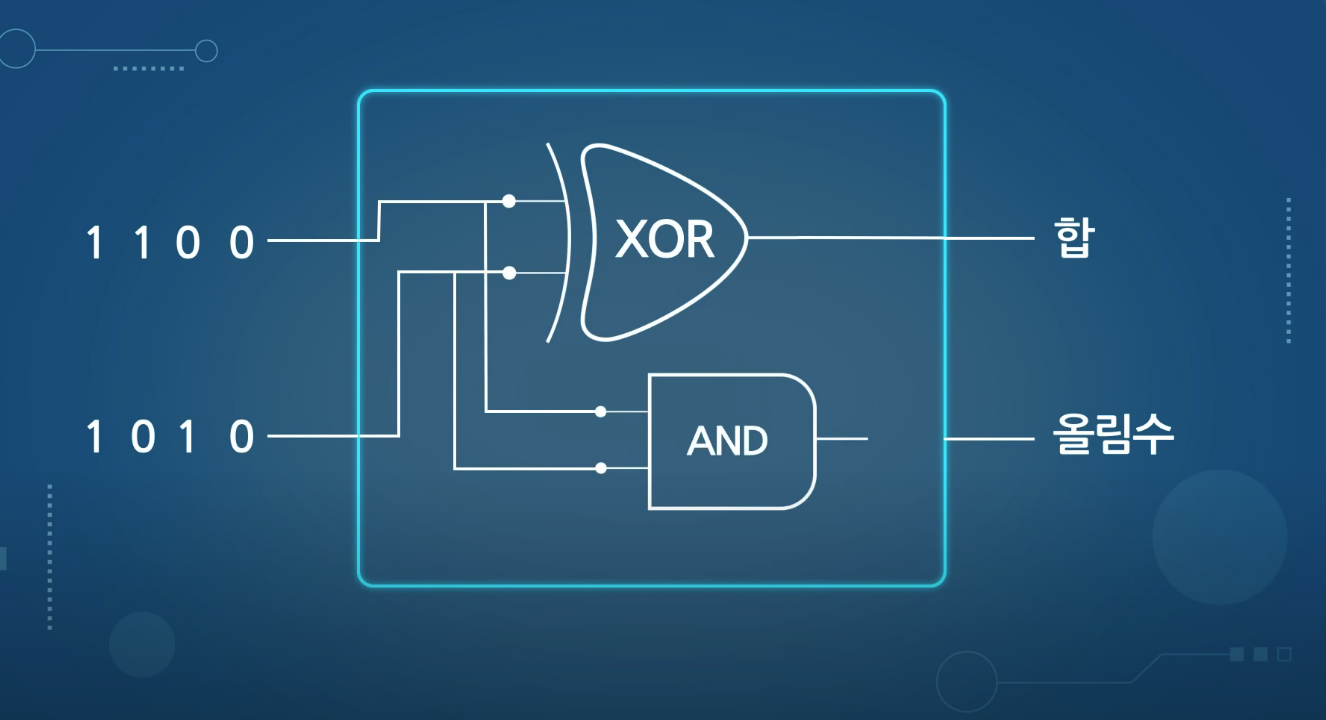

그럼 덧셈을 수행하는 원리를 알아보자

전류 출력 여부에 따라 0과 1로 이루어진

이진수 덧셈이 이루어지며

네 가지 경우로 나뉘며

이를 통해 두 출력의 합을 0, 1, 2로 구분할 수 있게 된다

합과 올림수는 각 XOR, AND 게이트의 논리와 동일하므로

이렇게 회로를 구성하면 더하기 게이트를 구성 가능

실제 덧셈에 사용되는 논리회로는 더 복잡하지만

이처럼 트랜지스터를 이용한다는 사실만 알아두자

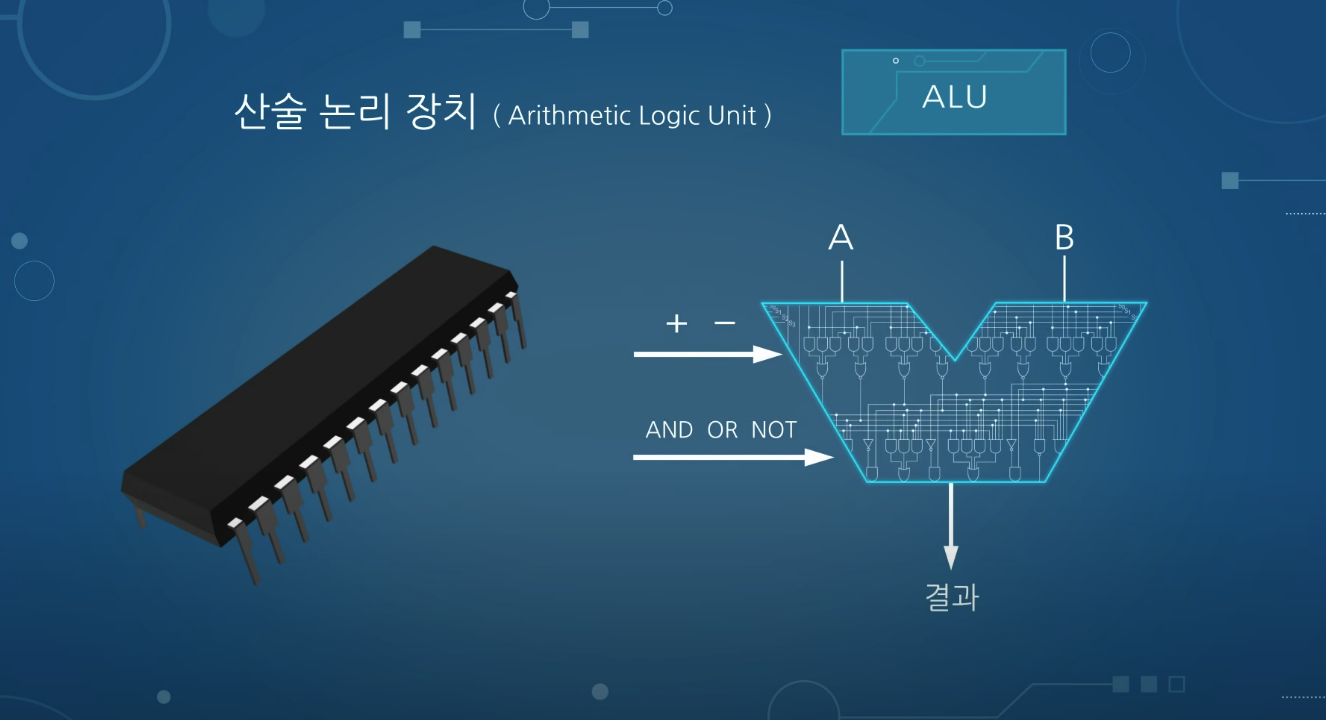

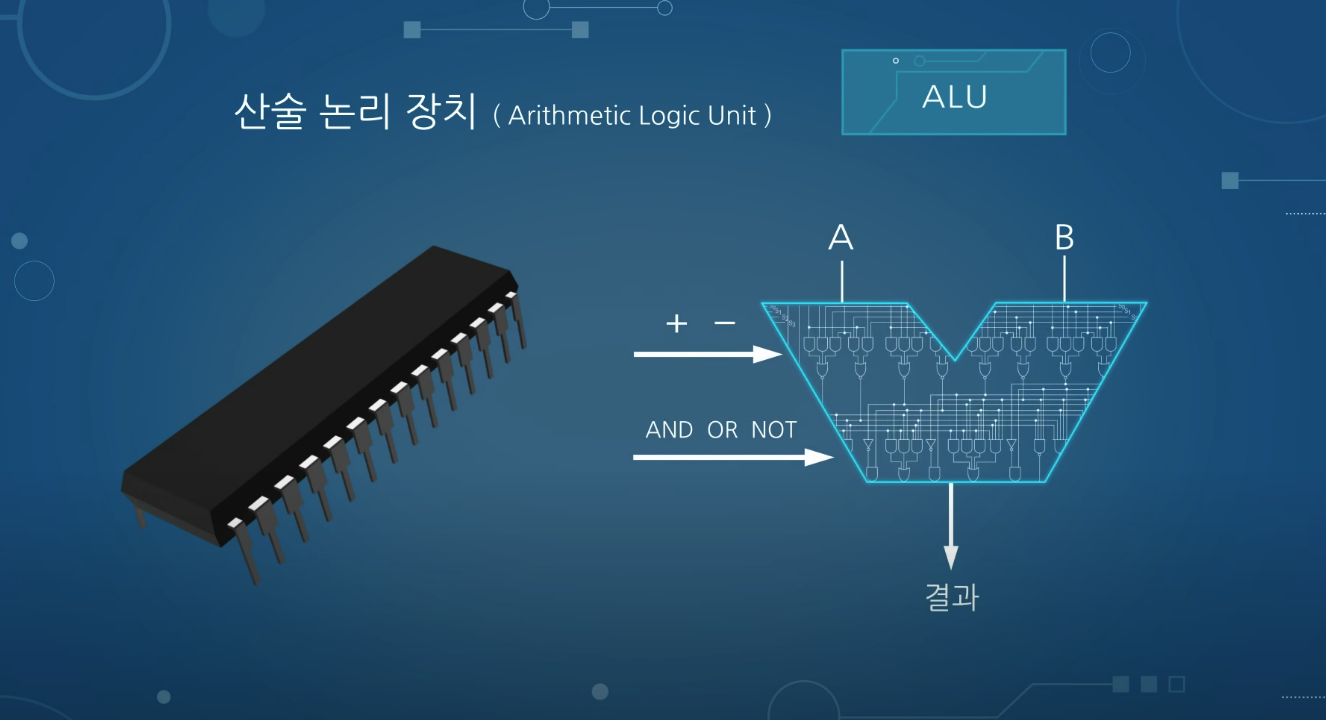

CPU에는 산술 논리 장치(Arithmetic Logic Unit), ALU가 있다

+, - 같은 산술과

AND, OR 같은 논리를 연산함

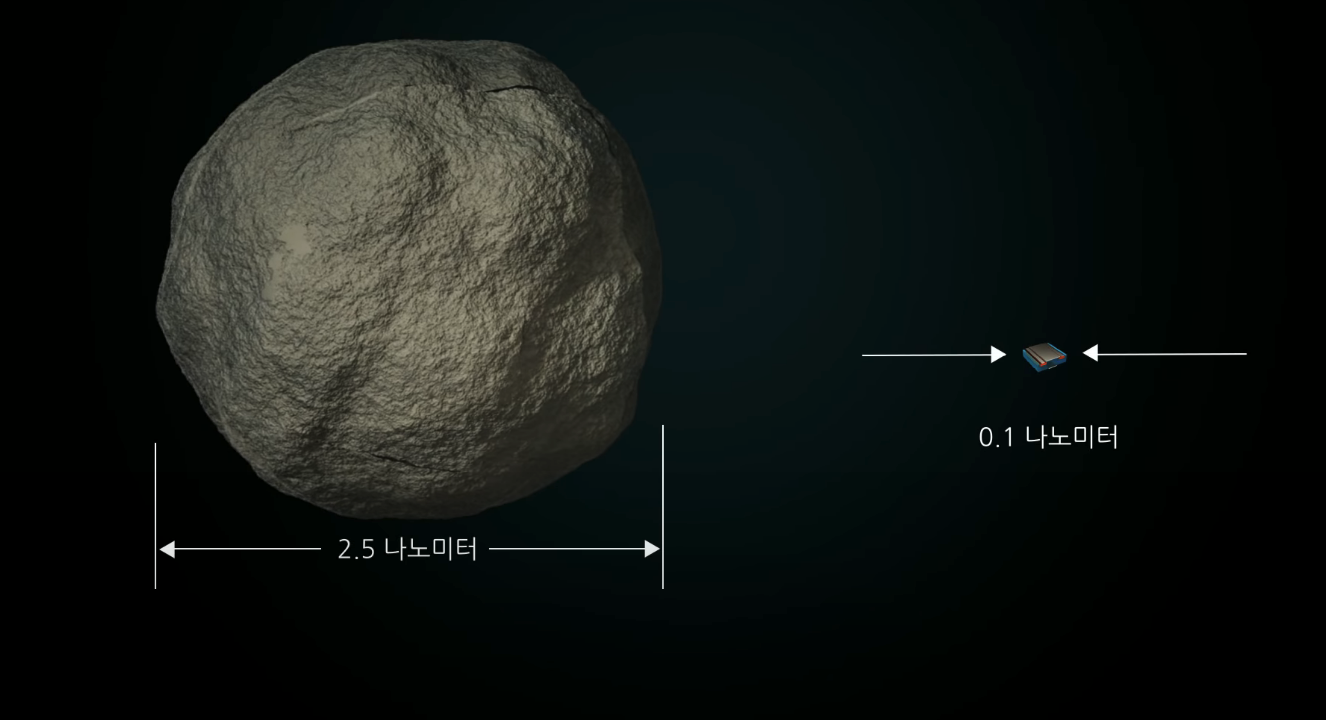

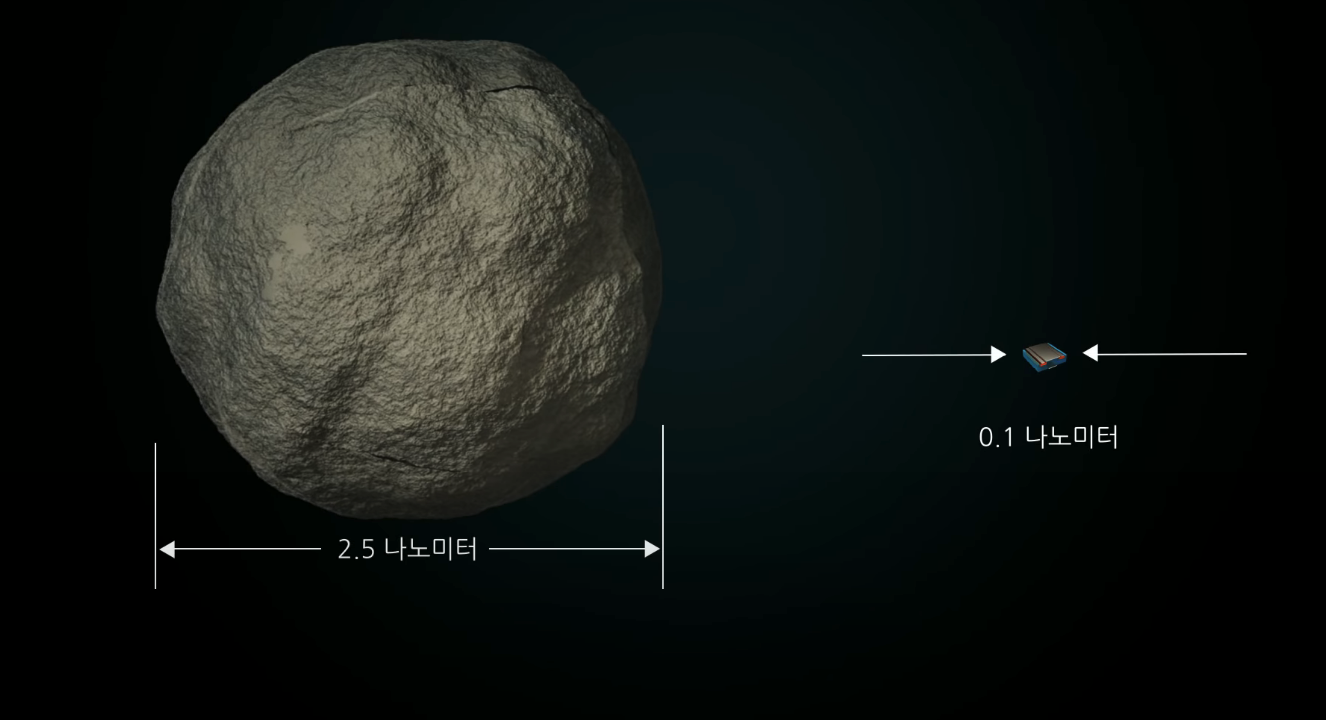

반도체는 전기를 끊었다 연결했다 ON/OFF 하는

수십억 개의 트랜지스터로 구성됨

CPU 안에 트랜지스터의 수가 충분하면 0, 1으로 모든 계산이 가능

=> 트랜지스터가 많을수록 성능 UP

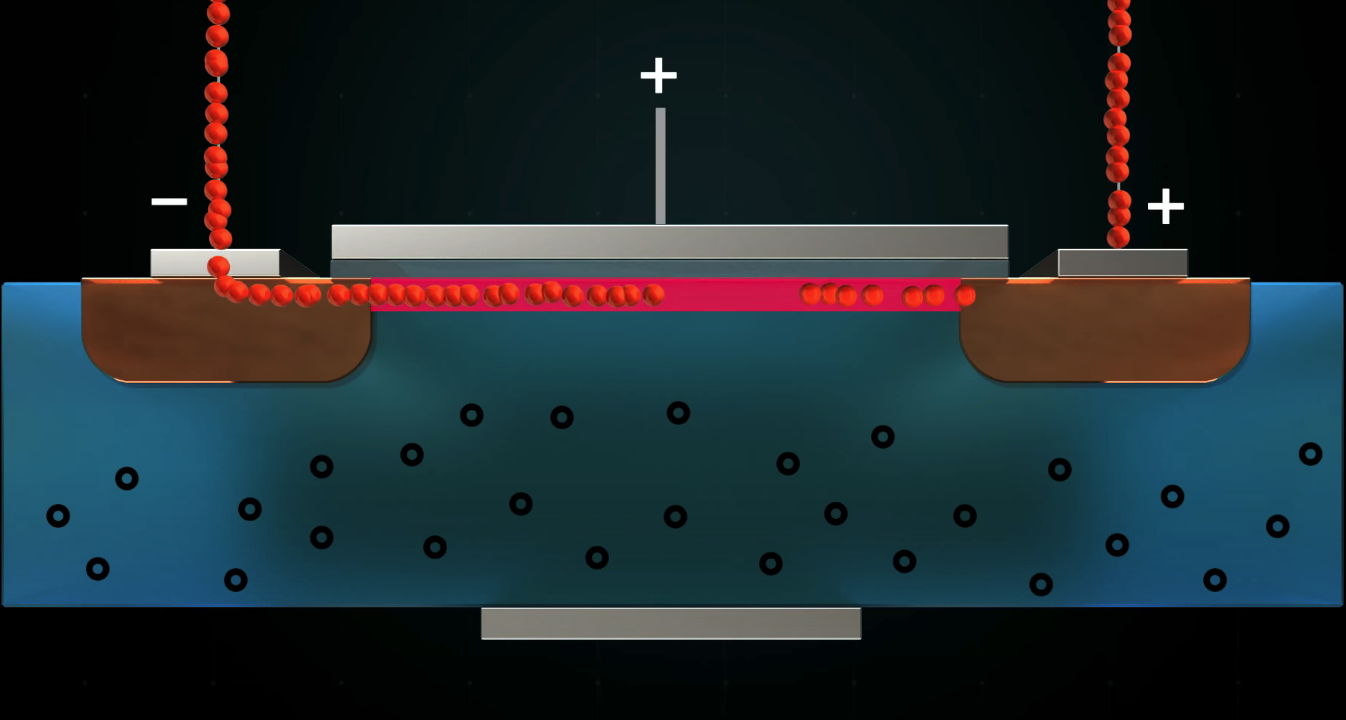

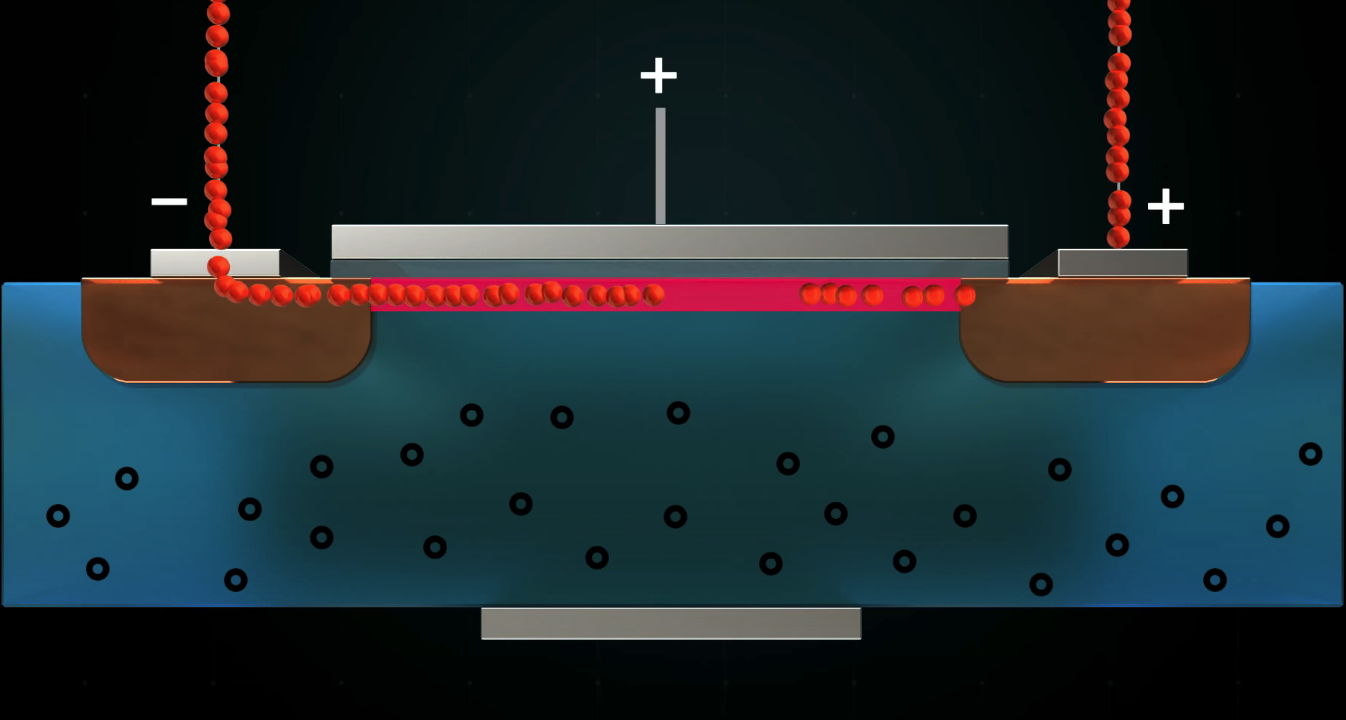

실제로는 미세먼지보다 작은 모스펫이라는 형태로 들어감

모스펫의 몸체는 반도체

위에는 전류가 흐르는 도체 존재

도체 부분에 전류를 걸어주면

전자들이 도체 쪽으로 밀집되고

여기에 전압을 걸어주면

+ 쪽으로 전자가 이동하면서

전류가 흐름

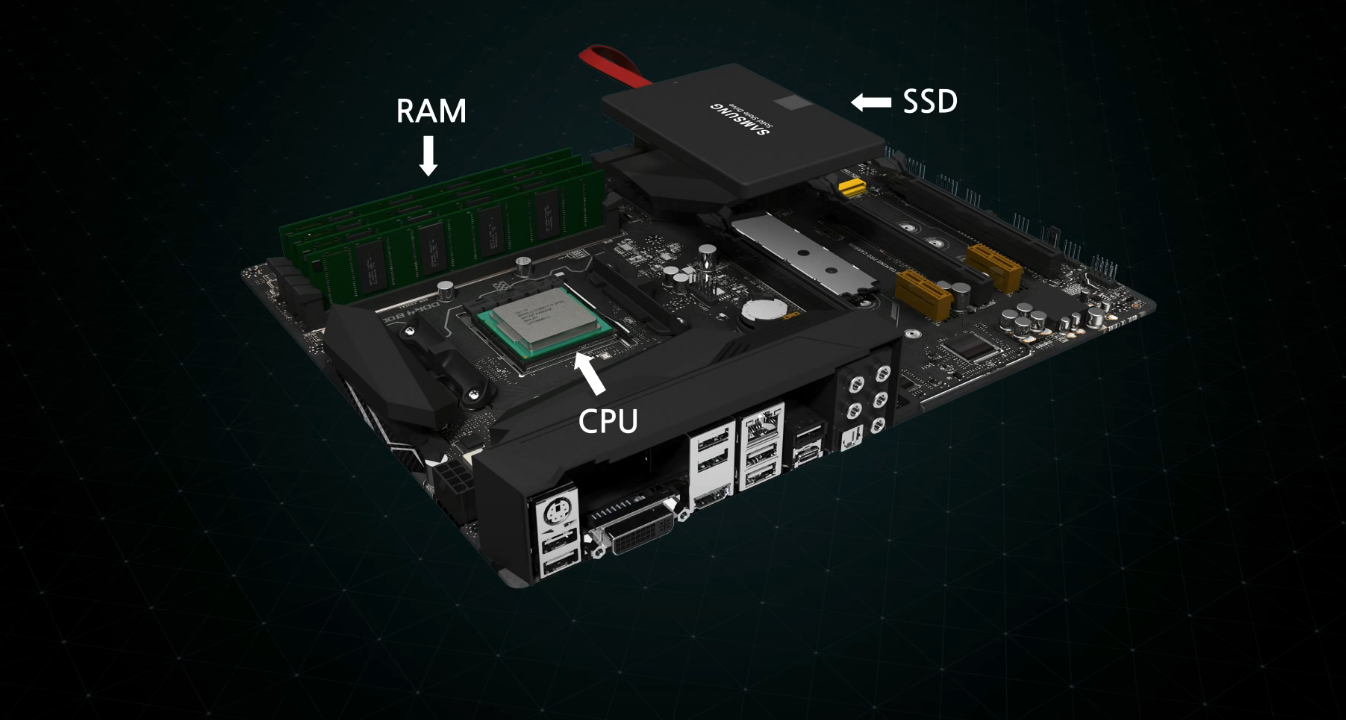

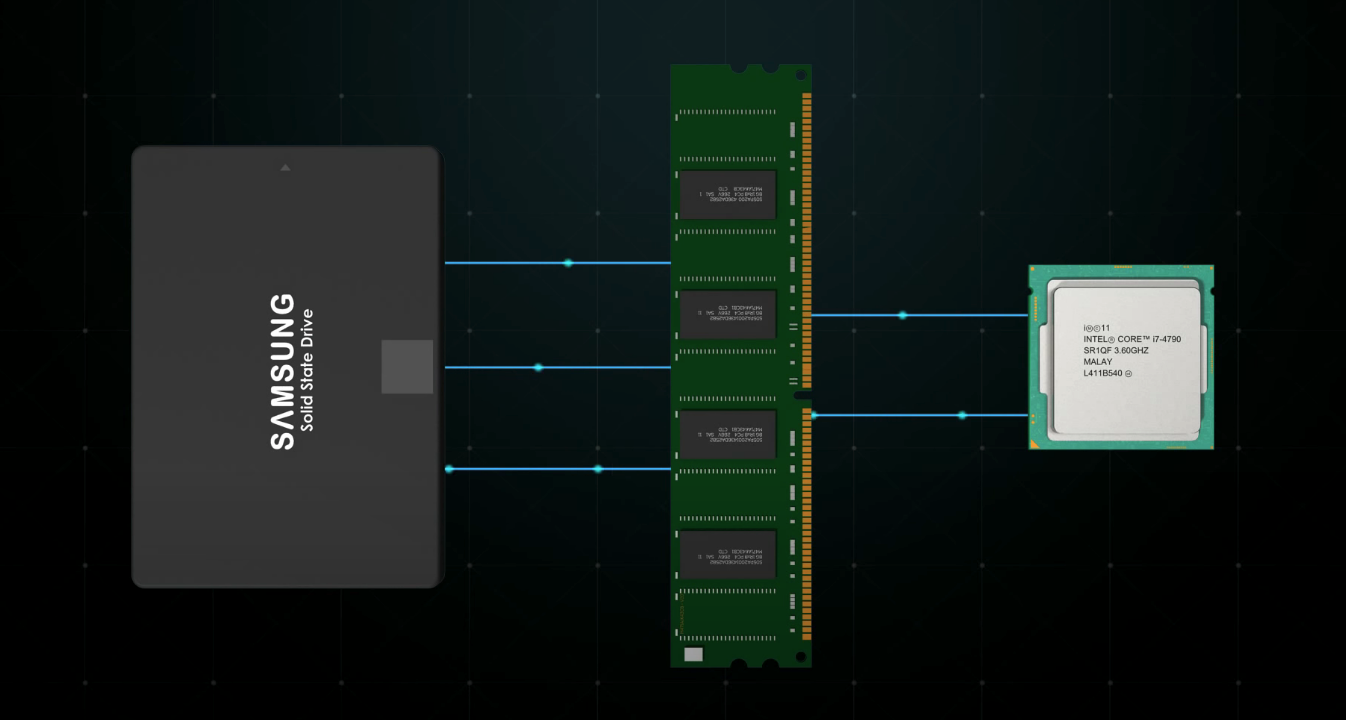

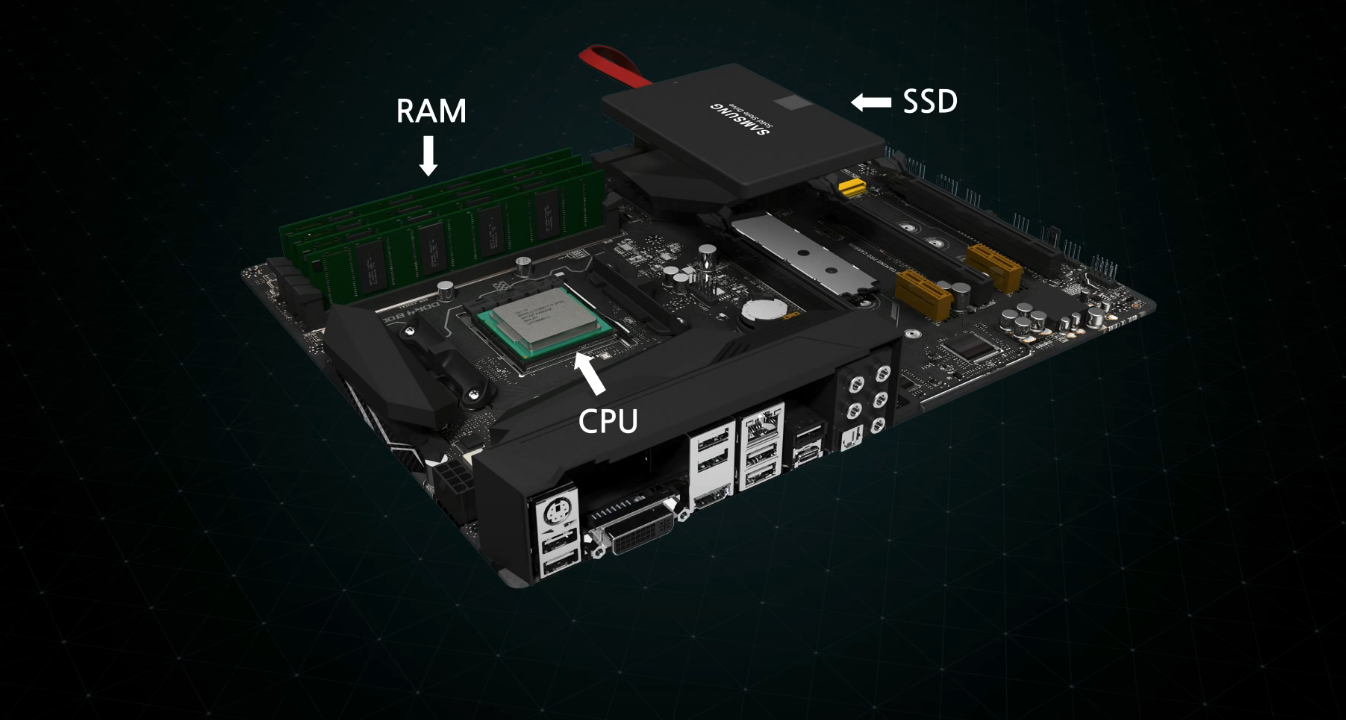

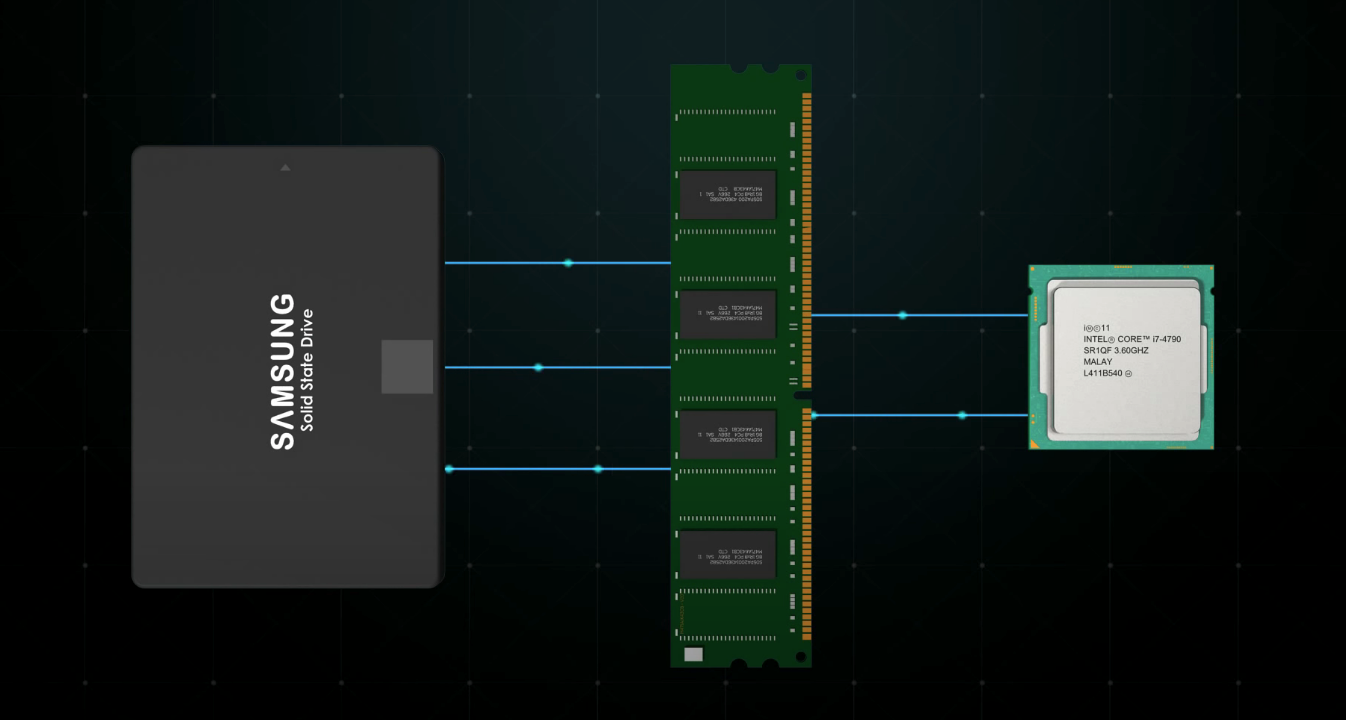

CPU, RAM, SSD가 보드에 존재하고

CPU는 느린 SSD와 직접 통신하지 않음

프로그램 실행 시, 데이터는 램으로 이동하고

CPU가 이를 가져감

RAM도 CPU보다 많이 느리기 때문에

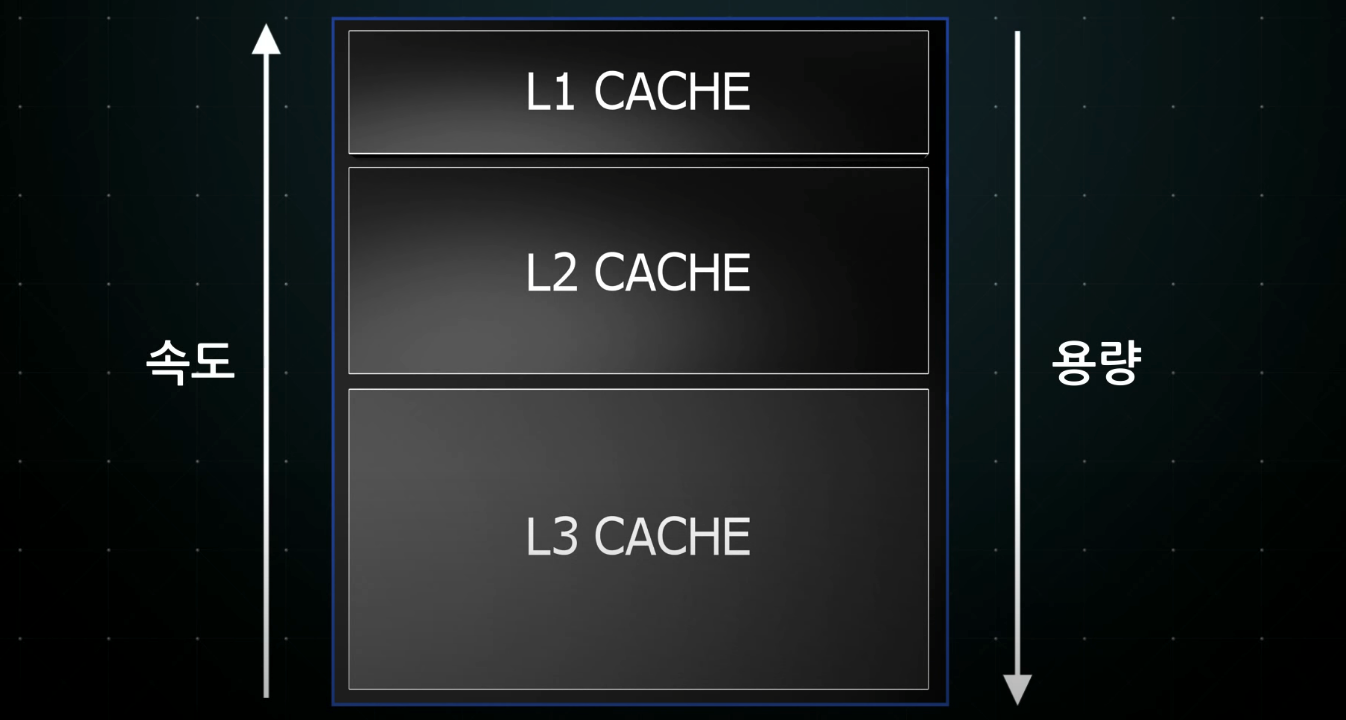

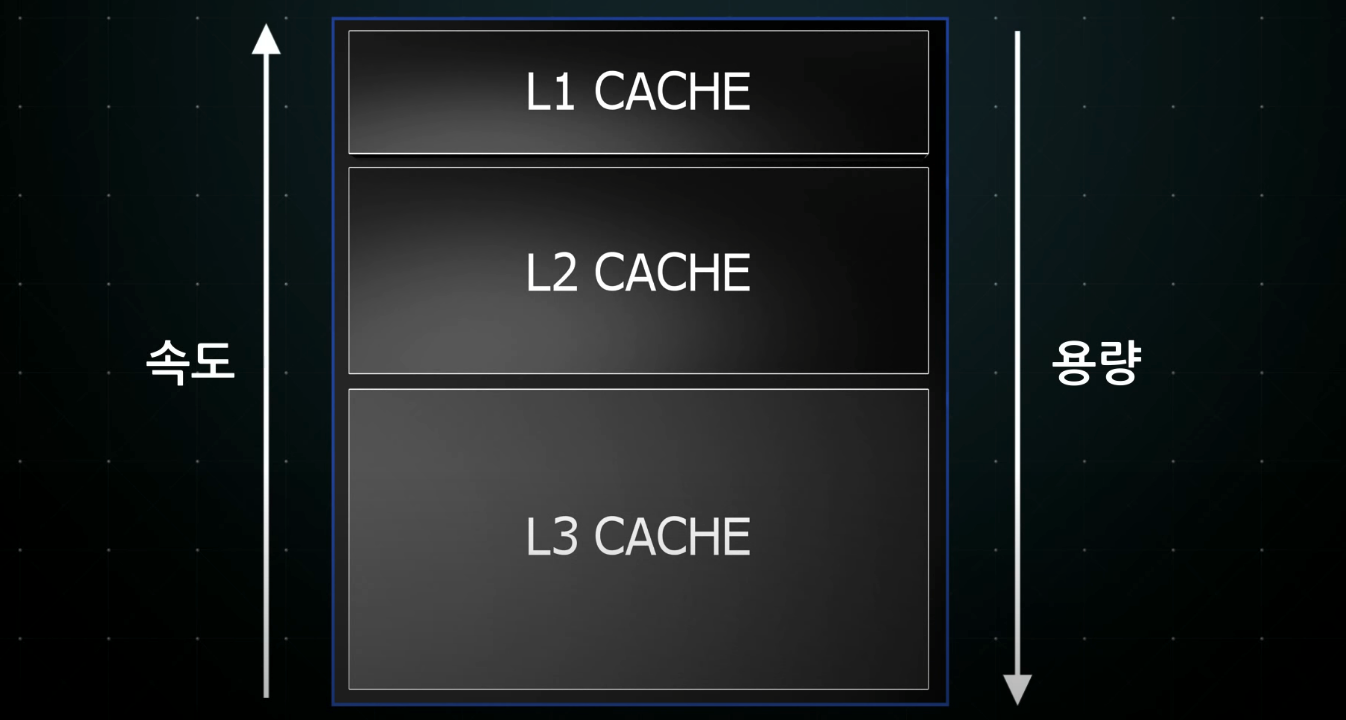

CPU 내부나 근처에 캐시 메모리를 가지고 있음

캐시 메모리는 용량이 적으므로 중요한 데이터만 저장하여 사용

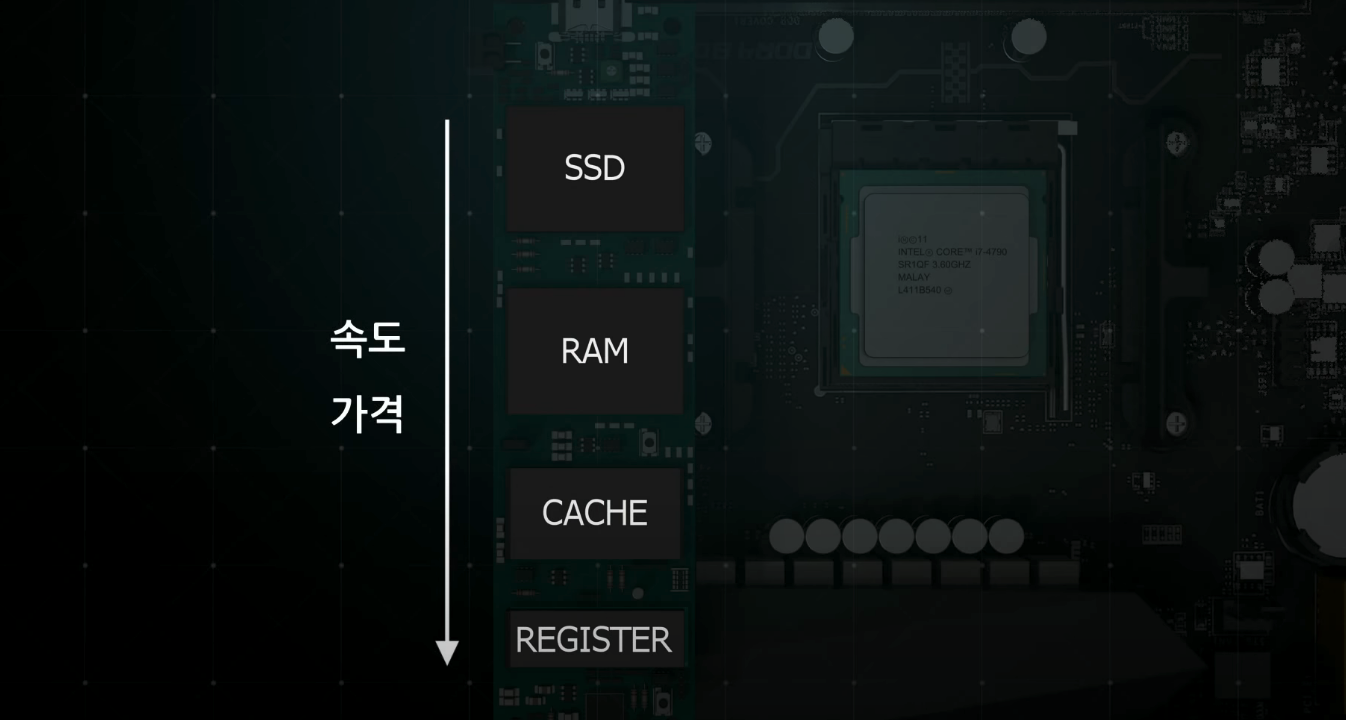

- CPU는 L1 -> L2 -> L3 -> RAM 순서로 원하는 데이터를 찾아봄

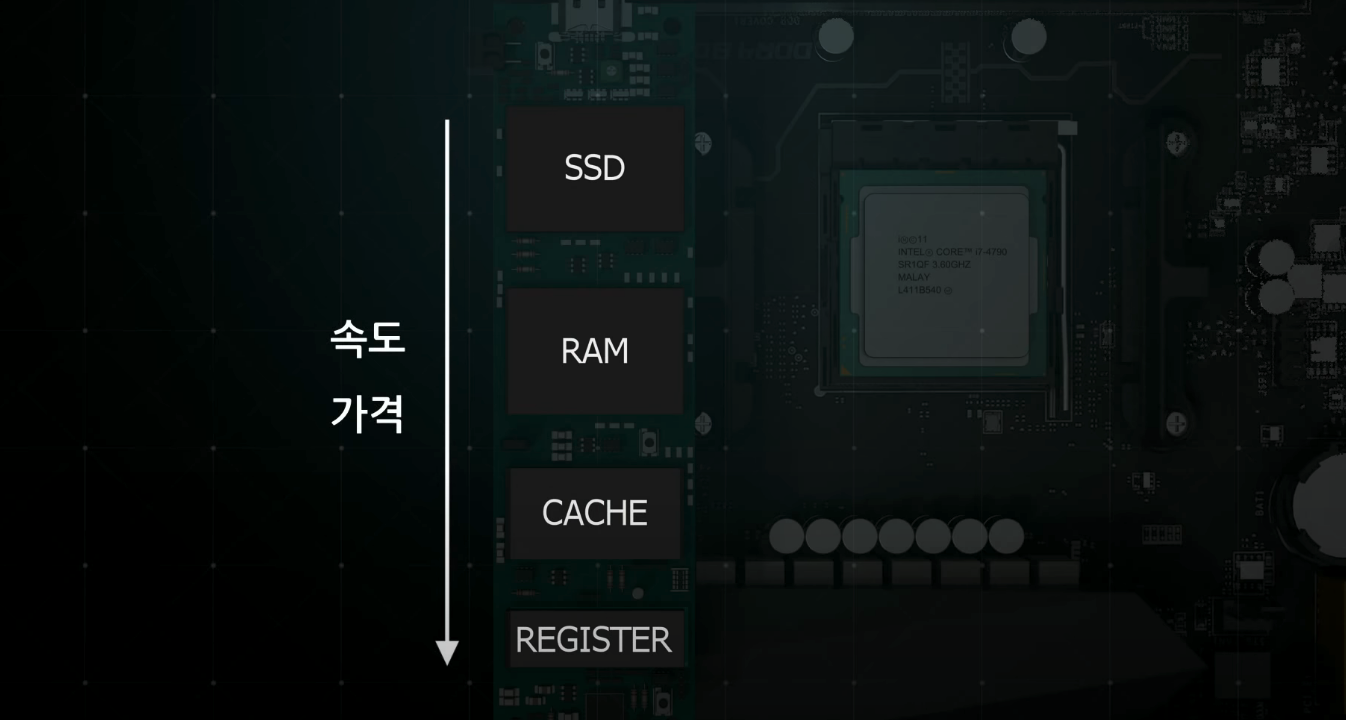

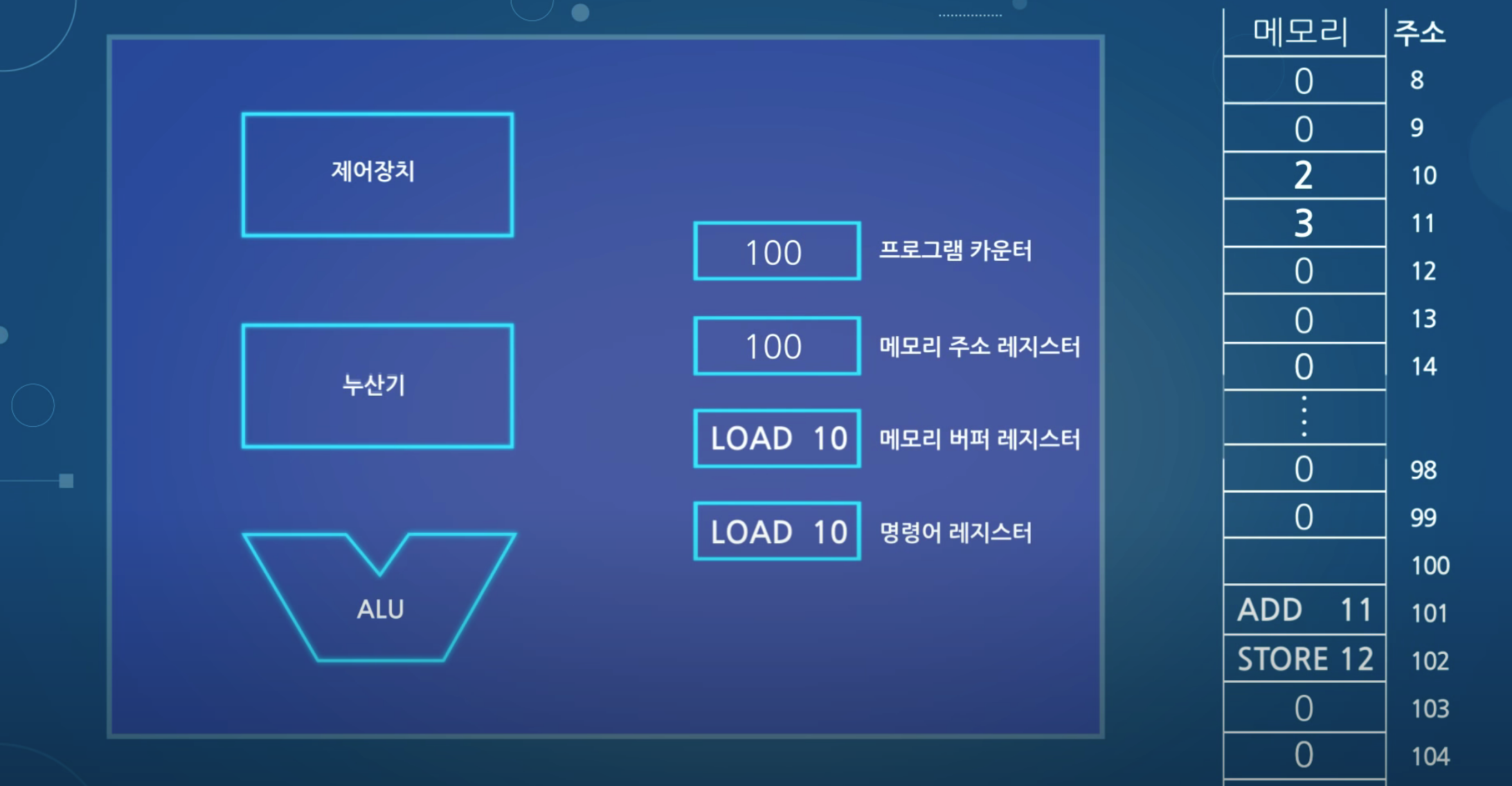

컴퓨터의 기억장치는 하드, 램, 캐시, 레지스터

- 레지스터 : CPU 내부에서 데이터를 일시적으로 저장하는 장치

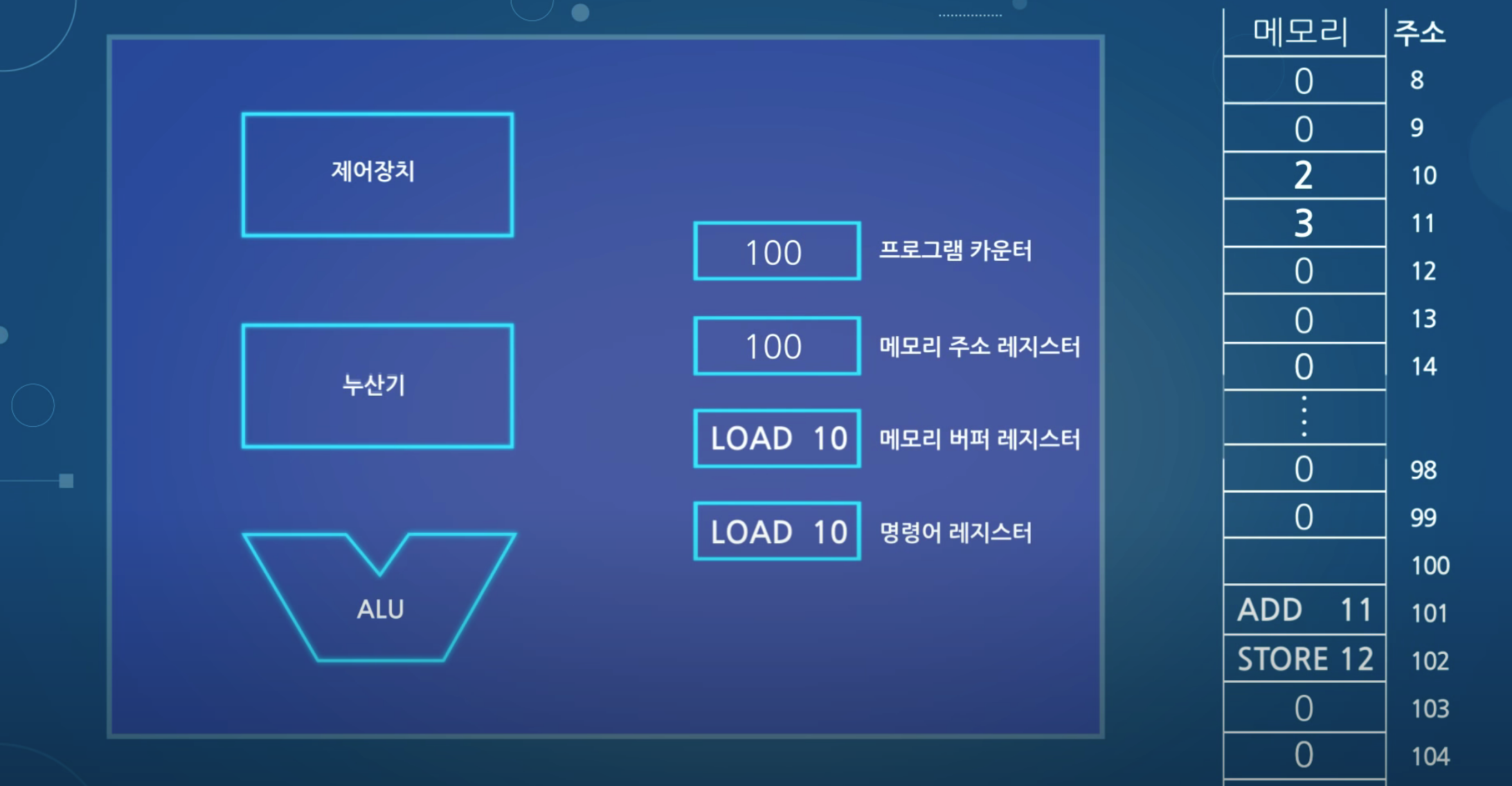

레지스터 동작 원리와 종류 (일부)

- 프로그램 카운터(PC) : 다음에 수행할 메모리의 주소

- 메모리 주소 레지스터 : PC로부터 수행할 주소를 넘겨받고, 해당 주소에서 데이터를 가져옴

- 메모리 버퍼 레지스터 : 메모리 주소 레지스터가 가져온 데이터나 명령을 일시적으로 저장

해당 메모리가 명령어 일 경우 명령어 레지스터로 전달하고

연산에 사용될 데이터인 경우 누산기 레지스터로 전달

- 명령어 레지스터 : 명령에 관한 데이터 저장

- 제어장치 : 명령어 레지스터에게 명령을 받아 해석하고 시스템에 지시를 보냄

- 누산기 레지스터 : 연산의 결과나 중간 값을 일시적으로 저장

최종 결과는 메모리 버퍼 레지스터로 전달되고, 메모리 버퍼 레지스터를 통해 메모리로 전달됨

- ALU : 산술 논리 연산을 수행

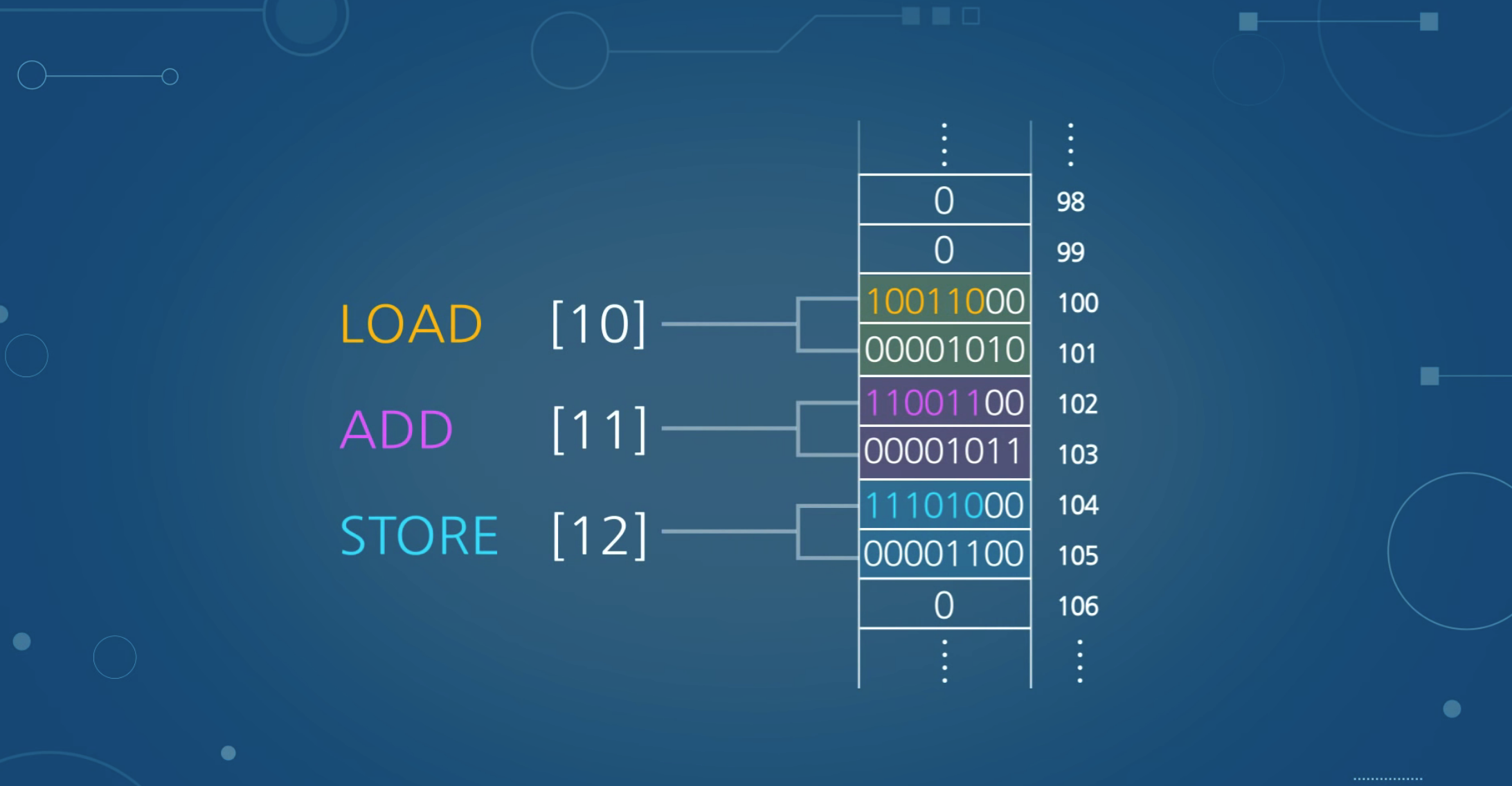

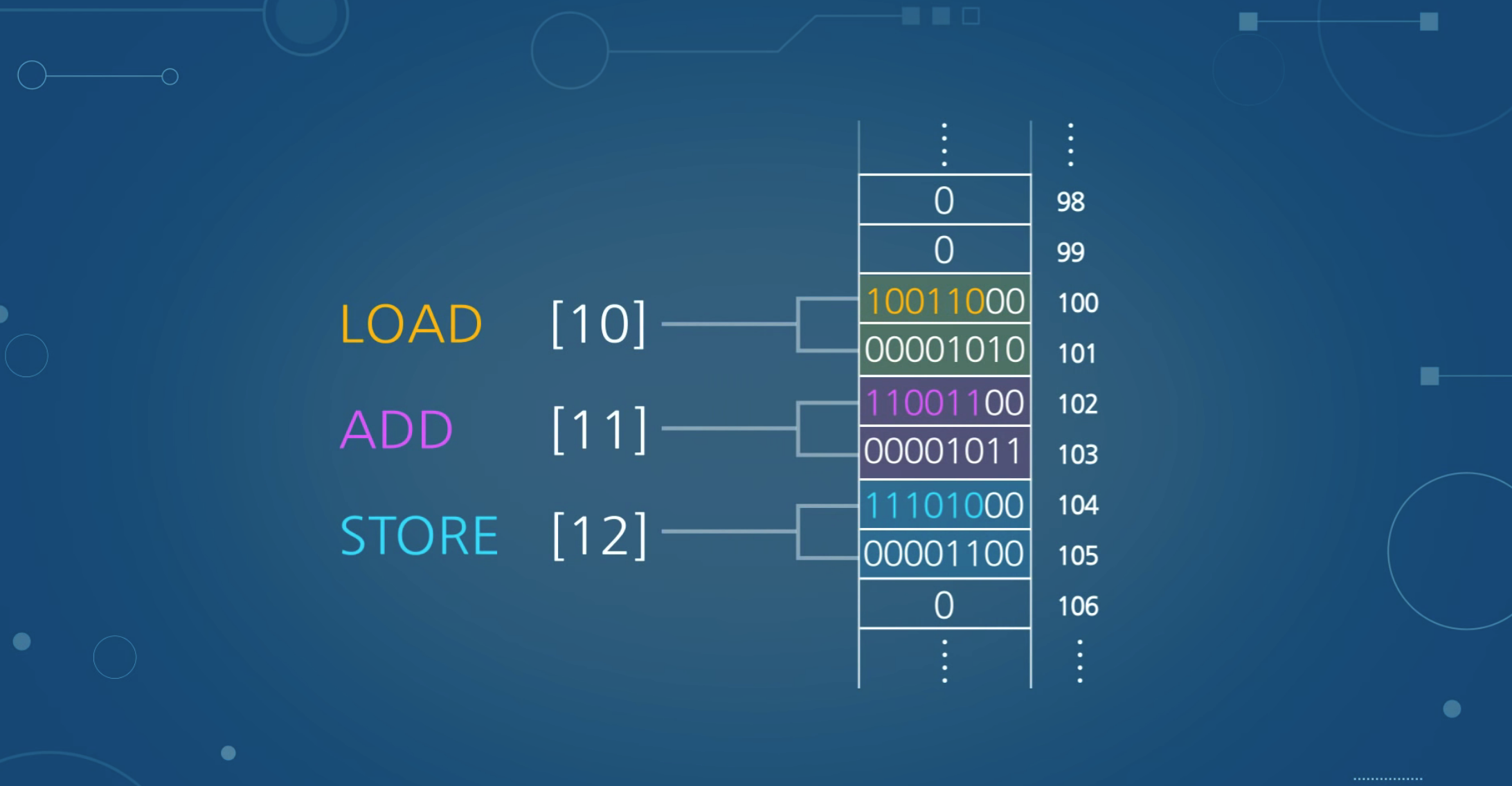

개발자가 프로그래밍 언어로 개발한 프로그램은

컴파일되어 어셈블리어로 변환됨

어셈블리어는 어셈블러에 의해 0과 1로 된 기계어로 다시 변환됨

앞의 명령어 부분은 6bit로 이루어짐

뒤의 데이터 부분은 10bit로 이루어짐

프로세서가 한 번에 처리할 수 있는 값이 16비트가 됨

여기서 프로세서가 한번에 처리할 수 있는 단위는 워드(Word) 라고함

(32bit CPU의 워드 : 32bit[4byte])

(64bit CPU의 워드 : 64bit[8byte])

따라서 각 범용 레지스터의 크기는 워드의 크기만큼 정해짐

32bit CPU의 PC 레지스터의 크기 : 4byte

64bit CPU의 PC 레지스터의 크기 : 8byte

32bit가 표현할 수 있는 숫자는 2^32이다

따라서, 메모리의 주소도 2^32개만큼 표시할 수 있다

램의 각 주소 당 기본 메모리 단위는 1 byte 이므로

1byte를 2^32개 만큼 가리킬 수 있으며

이는 1byte * 2^32 = 4GB가 된다

즉, 32bit CPU는 최대 4GB의 표현하고 사용할 수 있다

실제로는 메모리에 컴퓨터 운영을 위한

다른 데이터도 올라가기 때문에 3GB 정도를 사용할 수 있다

이와 같이 64bit OS는 2^64인 16 엑사바이트만큼의 메모리를 표시하나?

그만큼의 메모리 어드레싱을 할 필요가 없기 때문에

실제로는 하위 48bit만 사용

다시 돌아와서 16bit CPU 예를 보자

해당 기계어는 램에 위와 같이 저장됨

램은 8비트씩 저장하므로 두줄로 저장

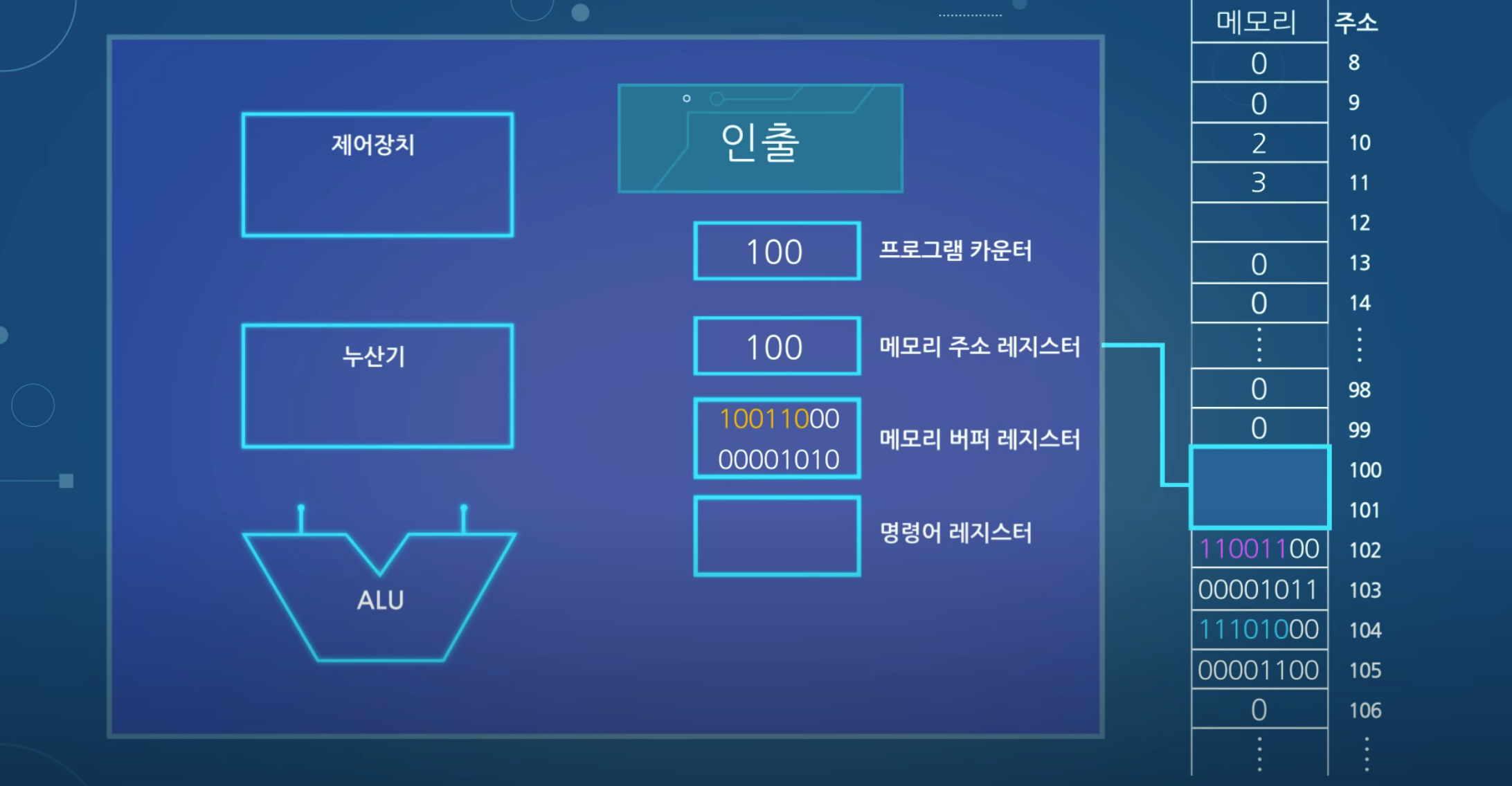

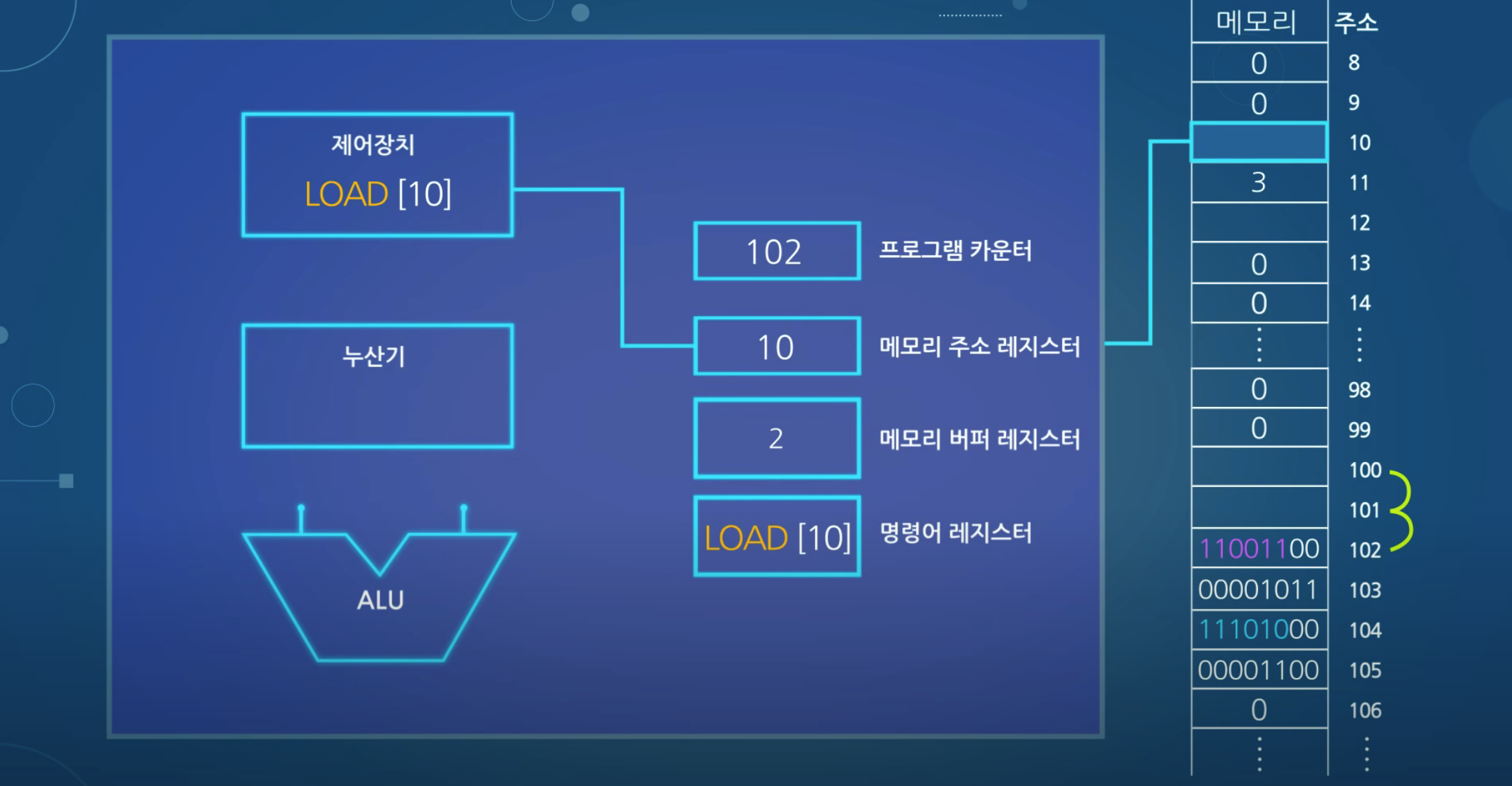

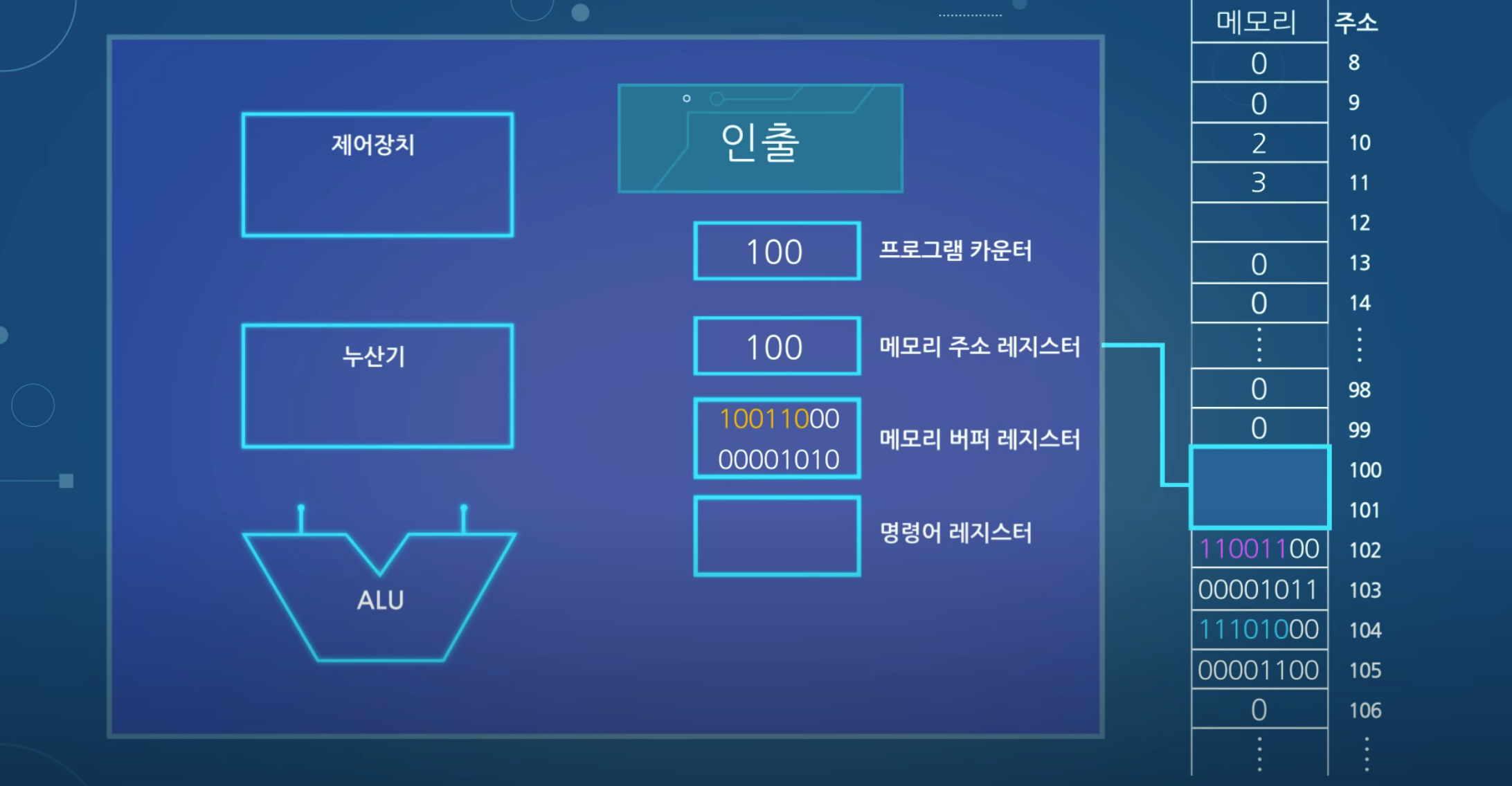

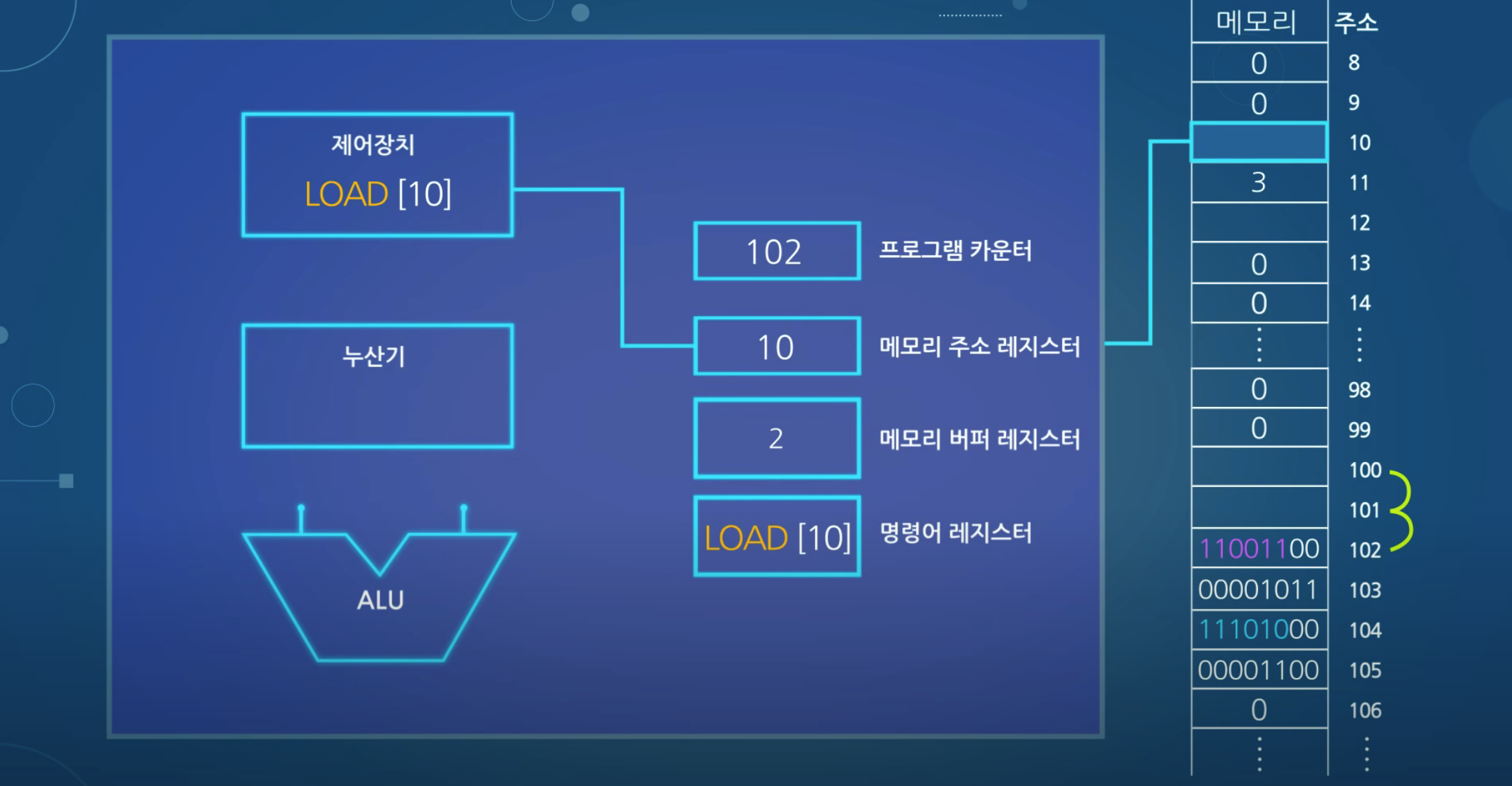

PC가 다음에 수행할 주소인 램의 100번 주소를 가리키고

메모리 주소 레지스터는 해당 명령 수행을 위해 100번 주소를 PC로부터 읽어옴

메모리 버퍼 레지스터는 100번째 주소의 값을 읽어와 저장

이 단계를 '인출'이라고 함

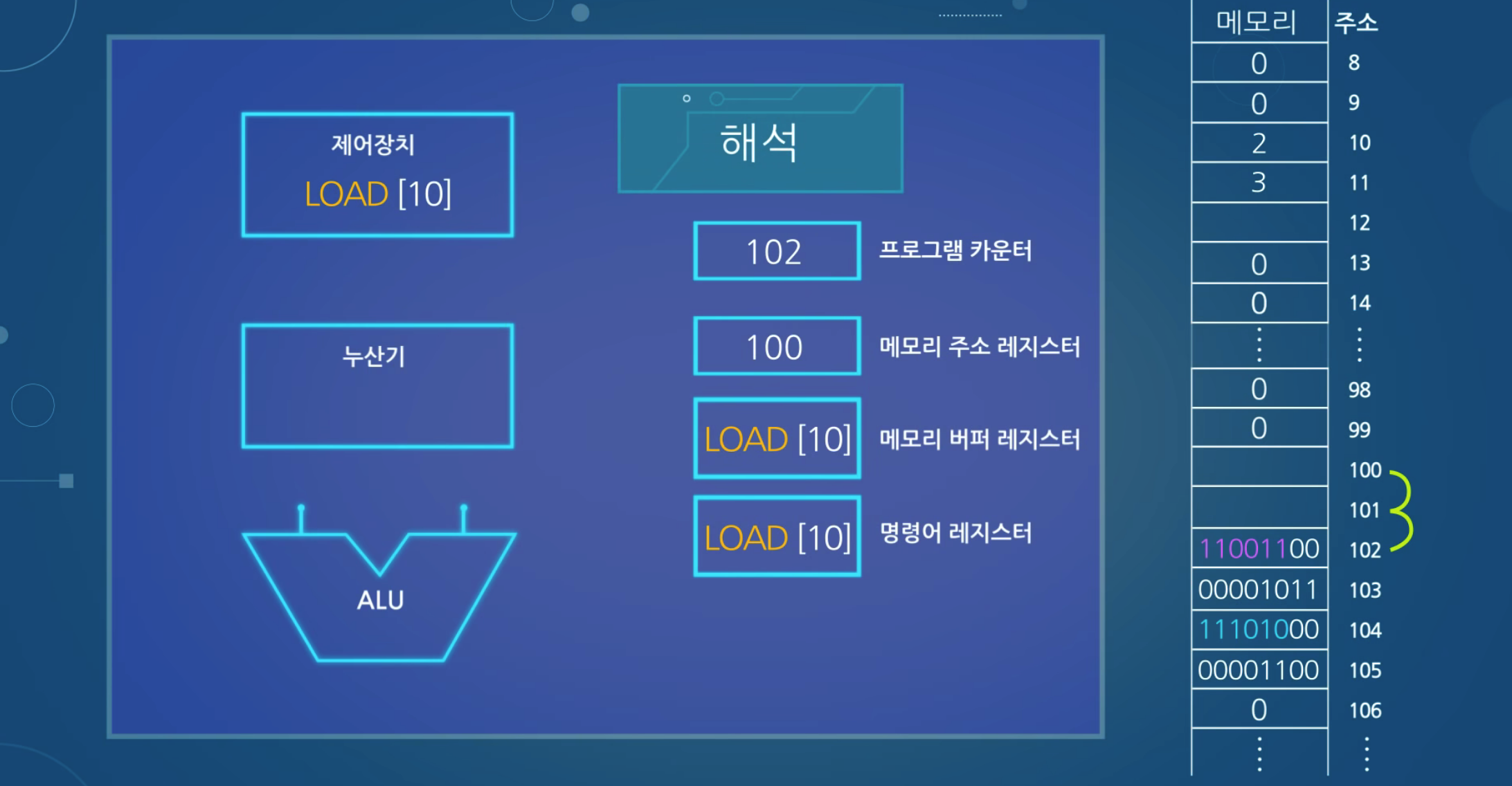

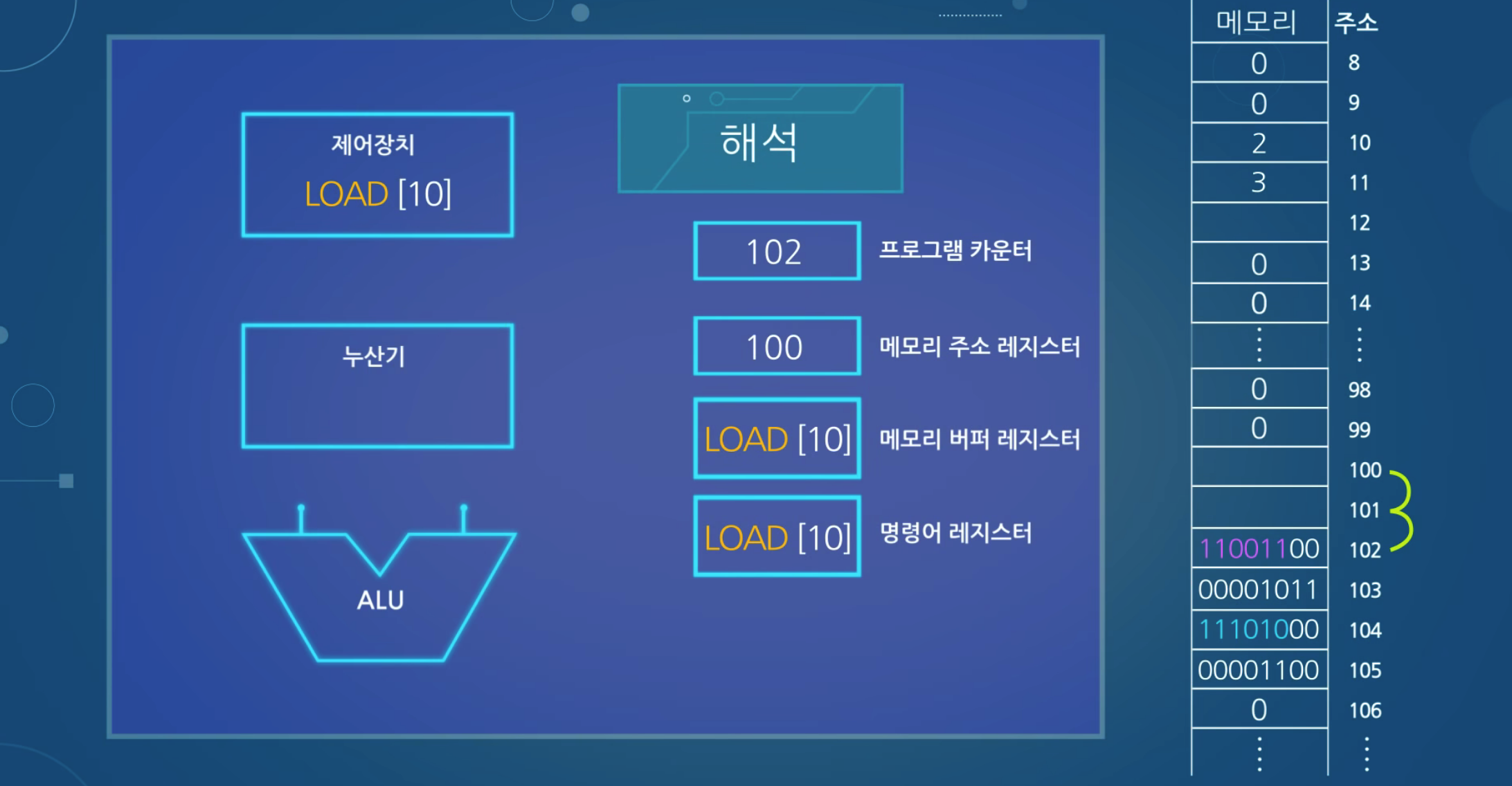

메모리 버퍼 레지스터에 저장된 데이터는 명령이기 때문에

명령어 레지스터에 저장

PC는 1 Word 만큼 증가(16bit CPU이므로 2byte만큼)

- 100 -> 102

명령어 레지스터에 저장된 명령은 제어장치로 이동되어 해석

이 단계를 '해석'이라고 함

제어장치의 명령은 10번째 데이터를 읽어 오는 명령이며

메모리 주소 레지스터에 읽어올 메모리의 주소(10번)가 저장되고

해당 주소(10번)에서 값을 읽어 메모리 버퍼 레지스터에 저장

10번 주소의 값은 명령어가 아닌 값(2)이므로 누산기 레지스터에 저장됨

여기까지가 명령어 LOAD[10] 한 줄의 처리 과정!

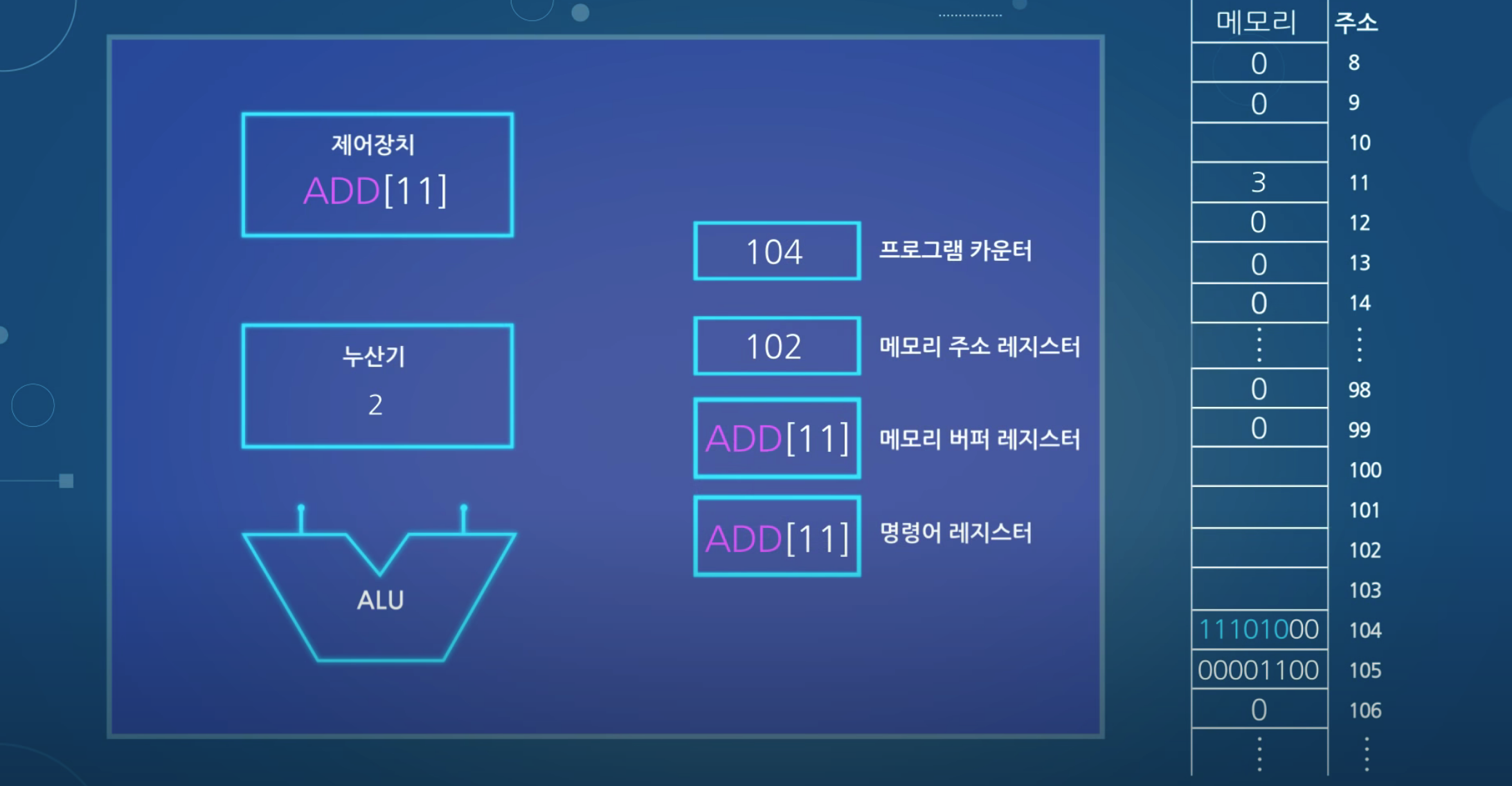

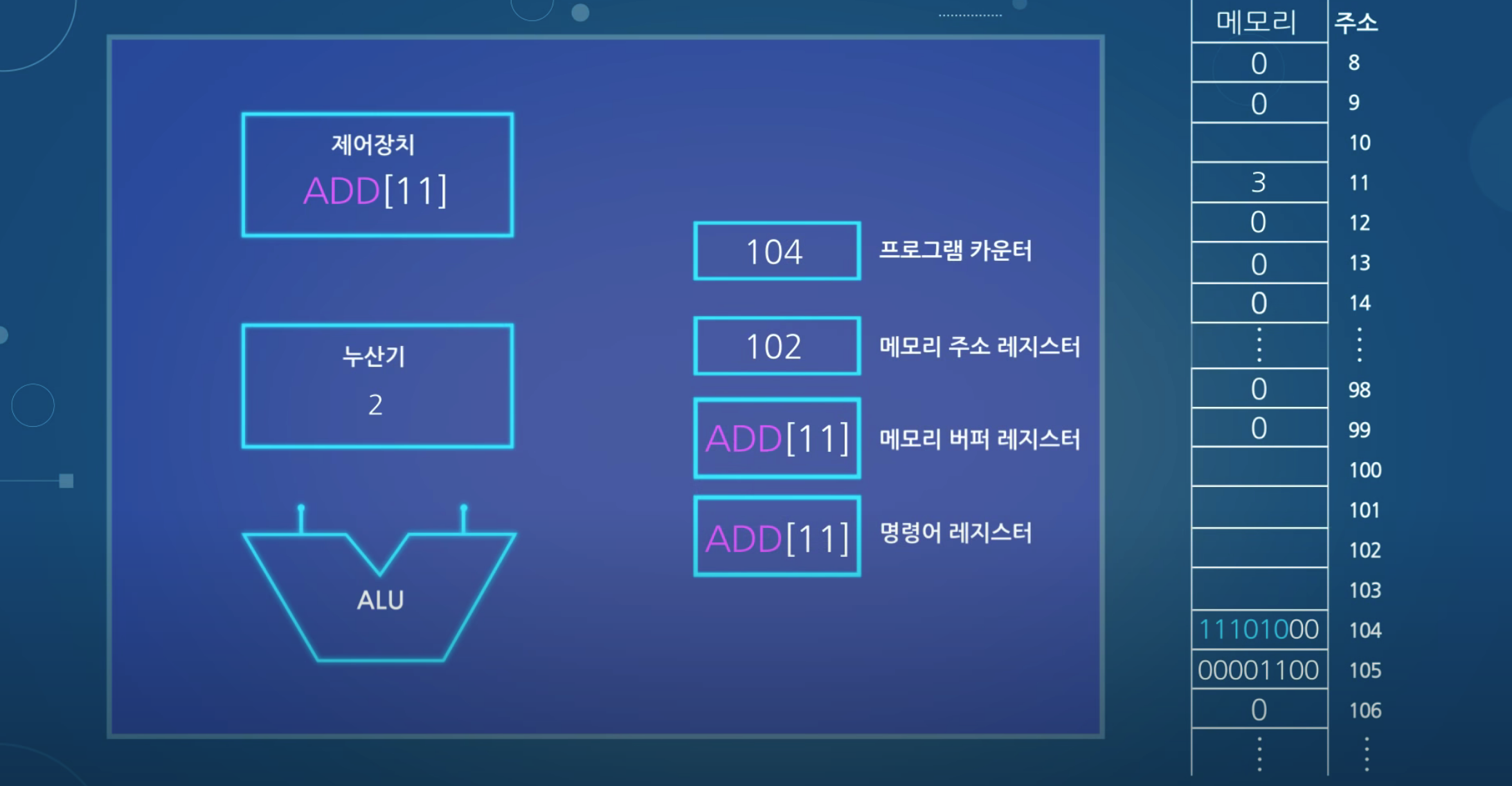

다음 처리를 위해 PC에 저장된 다음 실행할 주소(102)를 메모리 주소 레지스터로 가져옴

메모리 버퍼 레지스터를 통해 해당 값을 읽어오고

해당 값은 명령어이기 때문에 명령어 레지스터로 저장

명령어 레지스터의 명령 수행을 위해 제어장치로 저장

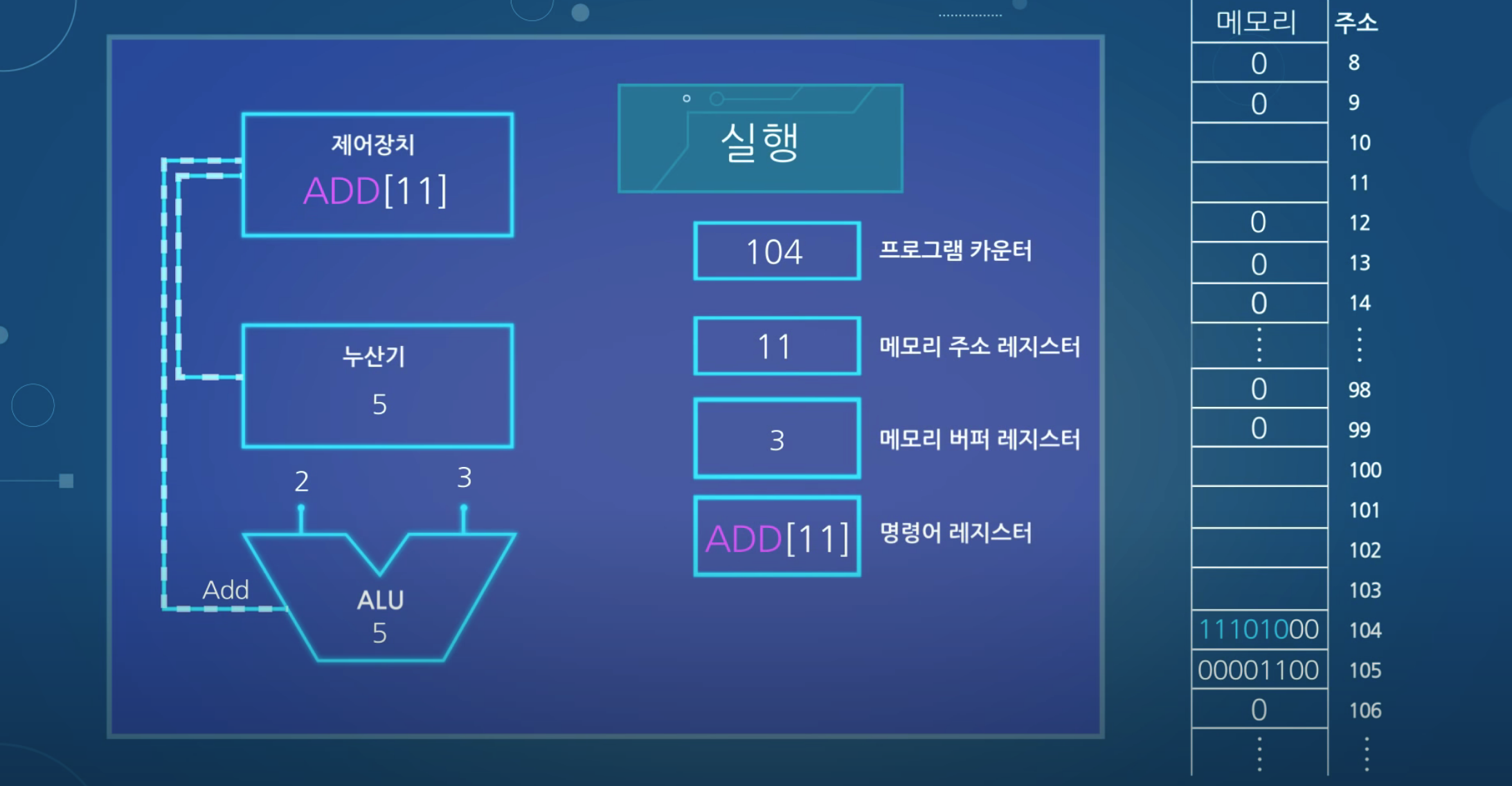

ADD 명령을 수행하기 위해 기존 누산기 레지스터의 값 2는

ALU로 전달

11의 값을 읽기 위해 메모리 주소 레지스터에 저장되고

읽어온 값은 메모리 버퍼 레지스터에 저장

해당 값(3)은 명령이 아닌 값이므로 바로 누산기 레지스터에 저장

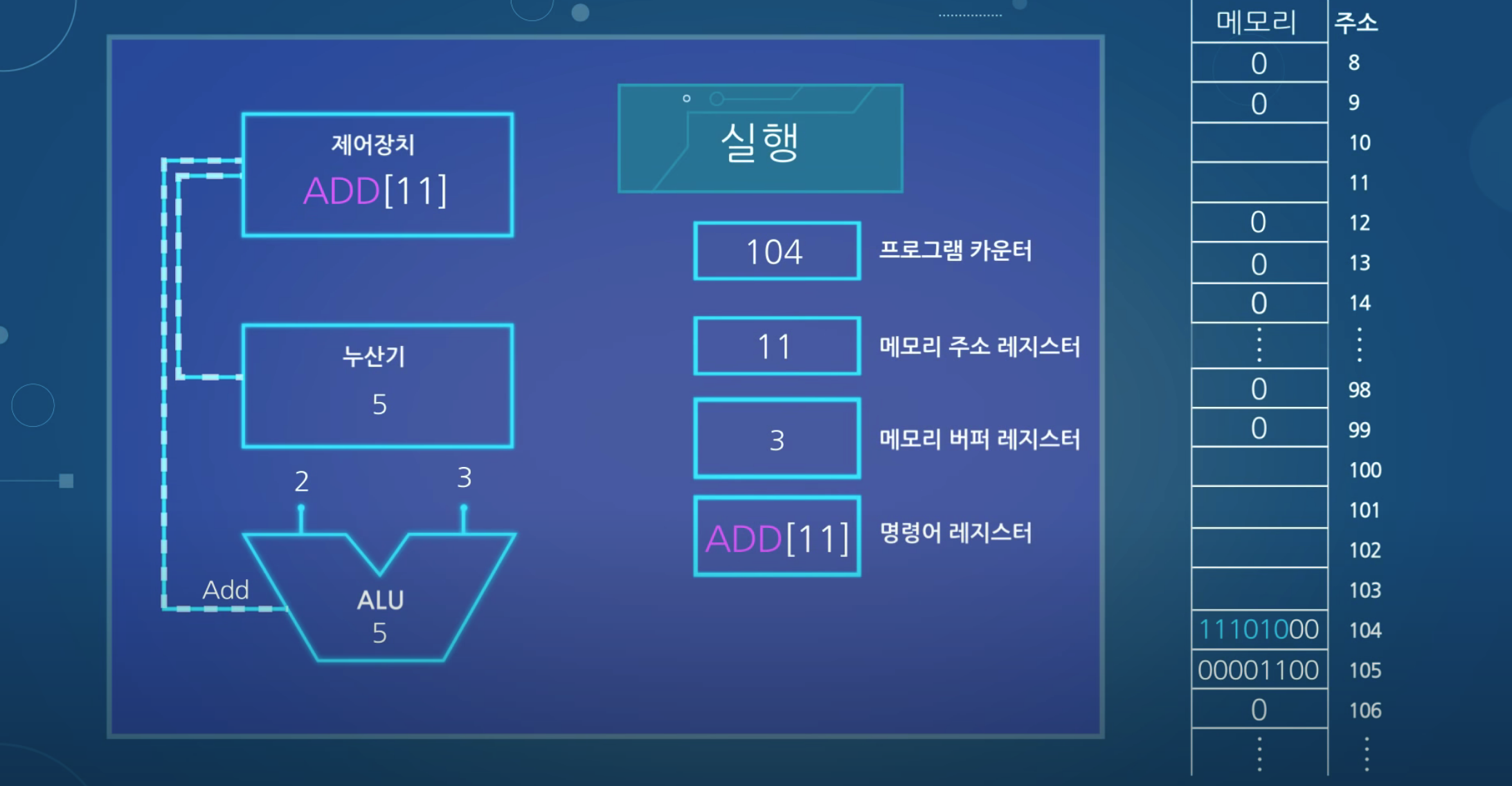

ALU에 의해 바로 2 + 3이 수행되고 값은 누산기 레지스터에 다시 저장

이 단계를 '실행'이라고 함

모든 과정은 제어장치를 통해 컨트롤됨

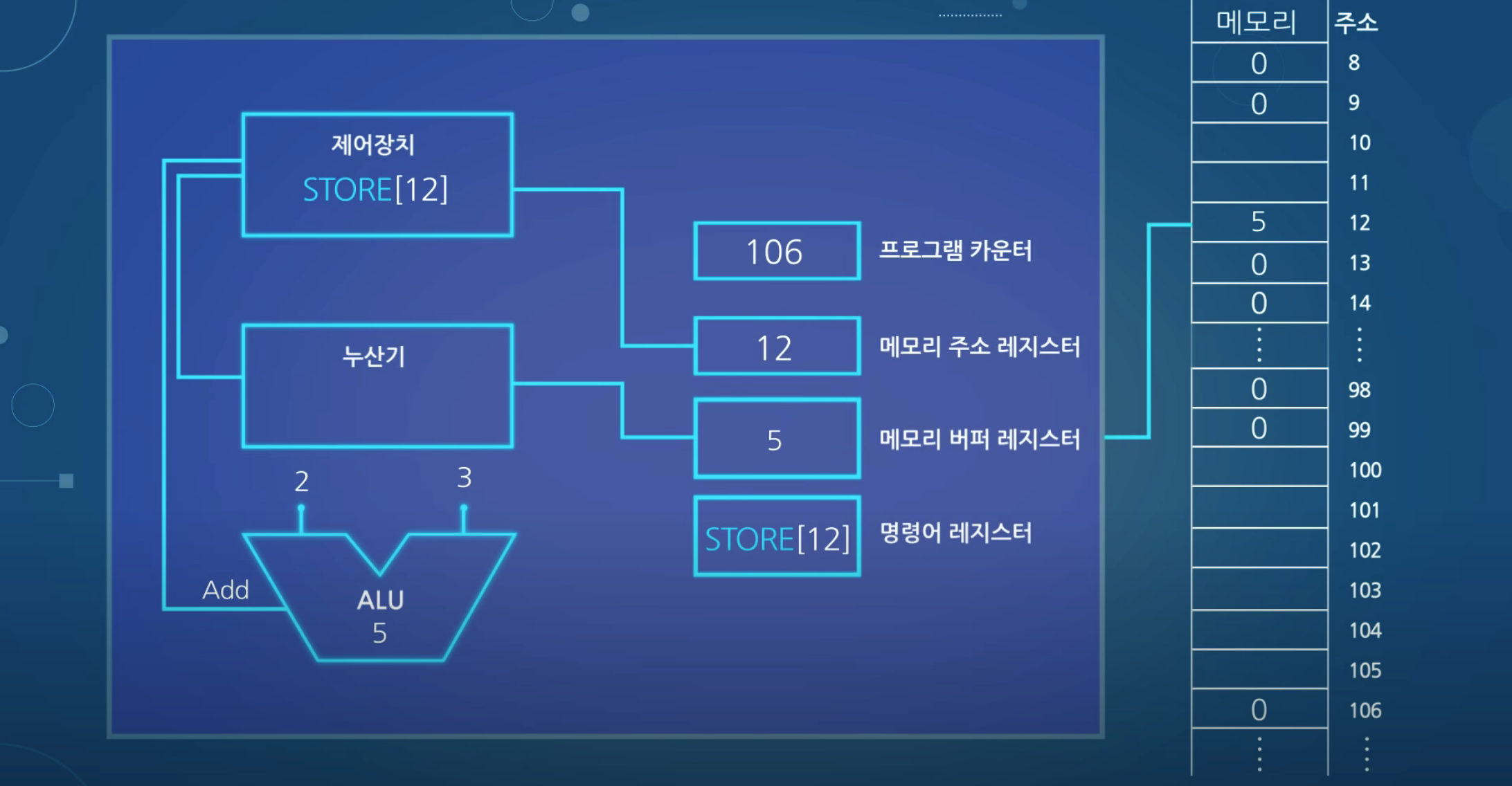

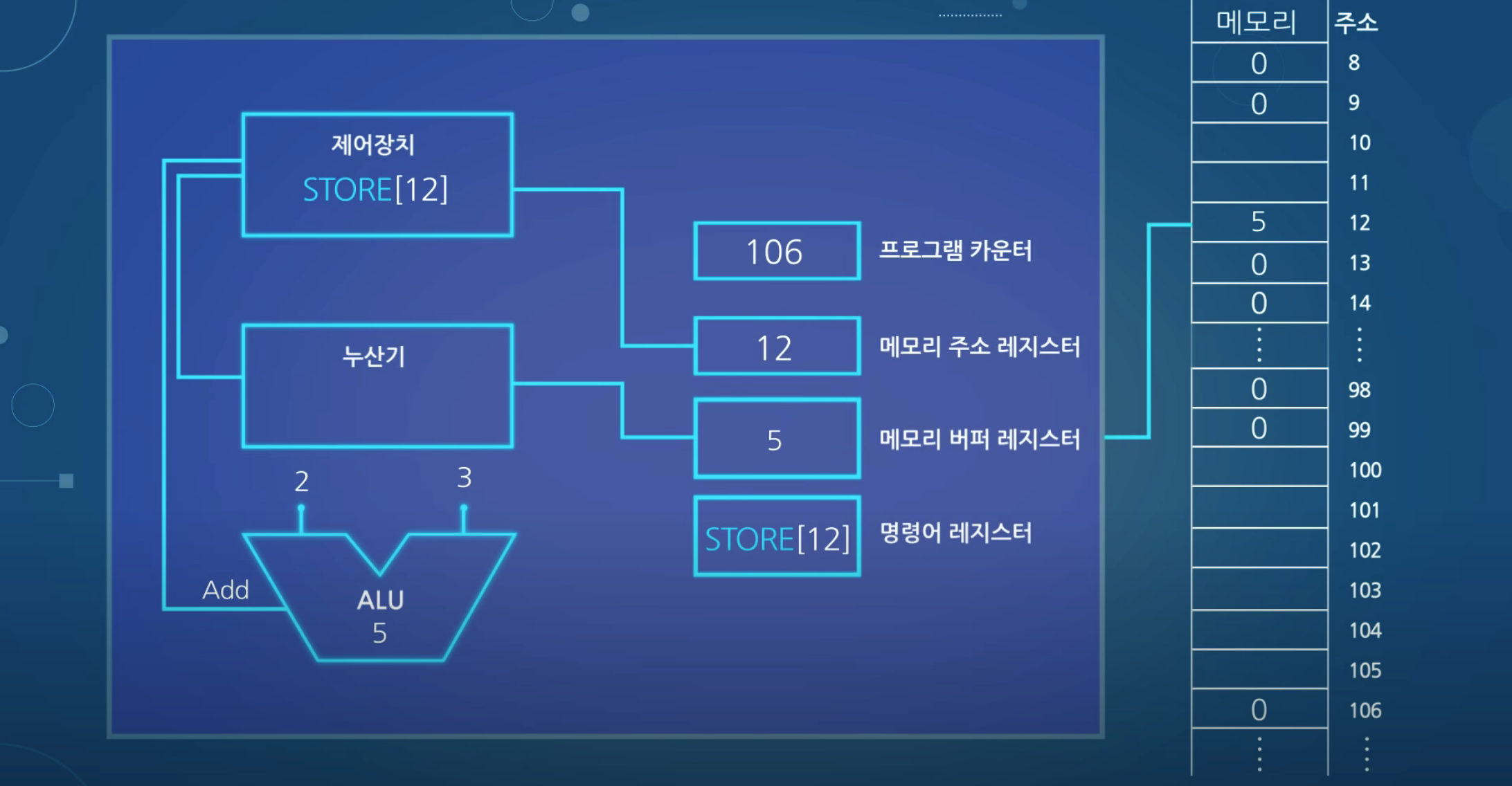

마지막으로 PC에 저장된 104번째 명령을 처리하기 위해

메모리 주소 레지스터가 104를 저장하고

메모리 버퍼 레지스터가 해당 주소의 값을 읽어옴

해당 값은 STORE[12]인 명령어 이므로

명령어 레지스터에 저장됨

저장하라는 명령이 제어장치에 저장

해당 명령 수행을 위해 메모리 주소 레지스터에 저장할 주소(12)가 저장

누산기 레지스터에 저장된 5가 메모리 버퍼 레지스터에 저장

해당 값이 지정된 주소(12)의 메모리에 저장

이와 같이 CPU는 인출 -> 해석 -> 실행 -> 저장하는 과정을 거침

각 과정은 여러 개의 쓰레드에 의해 처리되며

코어 하나에 여러 개의 쓰레드가 실행되면 속도가 빨라지고

코어가 많아지면 더 빨라진다~

아키텍처 디자인은 회사마다 다르며

팬티엄, 샌디브릿지, 하스웰, 타이거레이크 등

다양한 형태로 진화하고 있음

여기까지 정리해봅니다

학부생 때 연구실에서 WSN(Wireless Sensor Network)를 공부하였고

당시에 선배들의 가르침으로 각 기기의 회사가 제공하는 DataSheet에 따라

센서나 통신 장비가 동작하도록 회로를 구성할줄은 알았지만

내가 한땜질이 어떻게 동작하는지 내부적으로 너무 궁금했습니다

논리회로 책을 따로 사서 공부해보았고

당시 트랜지스터가 어떻게 동작하는지 이해가 안가서 반도체 공부까지 했었습니다

재밌게도 영상에 이런 노고들을 종합해 잘 설명해놨네요

(당시에 봤으면 더 편했을텐데ㅋㅋ)

논리회로 -> 반도체 이론 -> 컴퓨터 구조

내용이 전반적인 이해로 이어지는 설명이 마음에 들어 내용 보충하여 정리해봤습니다

큰맘먹고 정리해놨으니 종종 읽어볼 만하지 않나 생각해봅니다ㅎㅎ

참고한 영상입니다

https://www.youtube.com/watch?v=Fg00LN30Ezg

'Tech > Other' 카테고리의 다른 글

| JOSE(JSON Object Signing and Encryption) (4) | 2022.07.20 |

|---|---|

| GitHub Copilot 후기 (0) | 2021.11.26 |

| vMotion(Live Migration) (0) | 2021.11.23 |

| Duplex, Duplication(이중화) (0) | 2021.10.26 |

공부한 지 한참 돼서 가끔 헷갈릴 때가 있습니다

그중 CPU 관련 설명을 우연히 유튜브 영상 접했는데

그림으로 잘 설명되어 있고 회로 레벨부터 전반적으로 조립해주니 재밌네요

마침 연구실에서 센서네트워크 노드 땜질하면서

궁금해서 찾아봤던 정리해두었던 내용과 겹치기도 해서

영상 내용에 개인적으로 정리한 내용 보충하여 새로 정리해봅니다

CPU

- Central Processing Unit

- 중앙 처리 장치

- 기억, 해석, 연산, 제어 수행

CPU와 RAM은 반도체로 구성됩니다

- 도체 : 비저항이 작아 전기가 잘 통하는 물체

- 부도체 : 비저항이 높아 전기가 잘 통하지 않는 물체

- 반도체 : 도체와 부도체의 중간 정도로 전기가 통하는 물체

반도체는 주로 실리콘으로 구성

실리콘은 최 외각 전자가 4개

다른 실리콘 원자들과 전자를 공유하며 단단하게 결합됨

원자는 최 외각 전자가 8개 일 때 가장 안정적인 구조임

서로 안정적으로 단단하게 결합되어 있으면 전자가 이동하지 않음 => 전류가 흐르지 않음

즉, 순수한 실리콘은 전류가 통하기 어려움

때문에 실리콘보다 전자가 많거나 적은 원소를 첨가해 전류를 통하게 만들어줌

실리콘에 전자가 적은 원소를 첨가하면, 존재하는 전자들이 빈 곳으로 이동하며

전자의 이동 방향과 반대 방향으로 전류가 흐름

- 양공 : 양전하를 띈 구멍

실리콘에 전자가 한 개 많은 원소를 첨가하면, 남는 전자가 자유롭게 이동하며 전류가 흐름

전자가 많은 원소는 P(positive) 형 반도체

전자가 적은 원소는 N(negative) 형 반도체

P형과 N형 반도체 둘을 연결하면 N형의 남는 전자가

P형의 양공에 끌려 결합하게 됨

중성 상태로 시작한 P형 반도체 중 전자와 결합된 원자는 음전하가 됨

일정 순간부터 음전하 벽이 생겨 더 이상 전자가 넘어오지 못함

중성 상태로 시작한 N형 반도체 중 전자를 잃은 원자는 양전하가 되며

일정 순간부터 양전하 벽이 생겨 양공이 넘어오지 못함

이동 가능한 전자들이 없어지고 이를 공핍 영역이라 함

공핍 영역 가장자리에 서로 다른 전하를 가진 면이 생기고

+에서 -로 전기장이 생성됨

여기서 전지를 위와 같이 연결하면

P형 반도체의 양공이 -극 쪽으로(<-)

N형 반도체의 전자가 +극 쪽으로(->)

이동하게 되고, 공핍 영역이 확대되어 전하의 이동이 없어짐

위와 같이 전지를 반대로 걸어주면

P형 반도체의 양공이 -극 쪽으로(->)

N형 반도체의 전자가 +극 쪽으로(<-)

이동하게 되고, 전류가 흐름

물론 전자가 이동하다가 중간에서 공핍 영역을 만나지만

인공적으로 걸어주는 전압이 강해 넘어갈 수 있음

즉, 전류가 흐르게 하려면 같은 전하를 가진 전압을 연결하면 됨! = 순방향 연결

전류가 흐르지 못하게 하려면 반대 전하로 전압을 연결하면됨! = 역방향 연결

P형 N형 P형을 결합하고 N형 반도체를 얇게 구성

p-n(왼쪽)에는 순방향

n-p(오른쪽)에는 역방향

방향으로 전압을 걸어줌

양공이 p-n의 순방향 부분에서만 움직이며

해당 부분에만 전류가 흐름

순방향의 전압을 키우면

n이 얇으므로

세기가 공핍 영역의 반발력을 이겨

n-p 영역까지 넘어가는 양공이 생김

순방향의 전압이 세지면서 p-n-p 영역을 이르러 전류가 흐르게 됨

역방향의 전압을 키우면 흐르는 전류의 양이 더 많아지게 됨

즉, 전압의 일정 세기에 따라

반도체에 전류가 흐르게 할 수도, 흐르지 않게 할 수도 있음

해당 방식으로 스위치 작용을 해주는 반도체를 트랜지스터라고 함

트랜지스터는 일반적으로 이렇게 생겼으며

PNP, NPN 종류가 있음

트랜지스터는 Emitter(E), Collector(C), Base(B)로 구성

위에서 봤듯이 Base에 전류가 흐르면

NPN : C -> E로 전류가 흐름

PNP : E -> C로 전류가 흐름

즉, 가운데 도선(B)에 특정 전압을 걸어주면

전류가 흐름

이 트랜지스터를 이용하면

우리가 배운 논리회로를 구현할 수 있음

트랜지스터 두 개를 직렬로 연결해

각 Base 부분인 A, B에 전류의 여부에 따라

출력이 결정되며

이는 우리가 알고 있는 AND 게이트가 된다

트랜지스터를 병렬로 연결하면

우리가 알고 있는 OR 게이트이다

NOT 게이트는 출력을 트랜지스터 앞에 달면

Base에 전류가 없는 경우

출력으로 전류가 흐르고

Base에 전류를 흘려주면

트랜지스터 쪽으로 전류가 흐르게 됨

NOT 게이트

위에서 나온 게이트들을 조합하여 XOR 게이트 구성 가능

XOR 게이트

AND / OR / NOT 회로 도식화

그럼 덧셈을 수행하는 원리를 알아보자

전류 출력 여부에 따라 0과 1로 이루어진

이진수 덧셈이 이루어지며

네 가지 경우로 나뉘며

이를 통해 두 출력의 합을 0, 1, 2로 구분할 수 있게 된다

합과 올림수는 각 XOR, AND 게이트의 논리와 동일하므로

이렇게 회로를 구성하면 더하기 게이트를 구성 가능

실제 덧셈에 사용되는 논리회로는 더 복잡하지만

이처럼 트랜지스터를 이용한다는 사실만 알아두자

CPU에는 산술 논리 장치(Arithmetic Logic Unit), ALU가 있다

+, - 같은 산술과

AND, OR 같은 논리를 연산함

반도체는 전기를 끊었다 연결했다 ON/OFF 하는

수십억 개의 트랜지스터로 구성됨

CPU 안에 트랜지스터의 수가 충분하면 0, 1으로 모든 계산이 가능

=> 트랜지스터가 많을수록 성능 UP

실제로는 미세먼지보다 작은 모스펫이라는 형태로 들어감

모스펫의 몸체는 반도체

위에는 전류가 흐르는 도체 존재

도체 부분에 전류를 걸어주면

전자들이 도체 쪽으로 밀집되고

여기에 전압을 걸어주면

+ 쪽으로 전자가 이동하면서

전류가 흐름

CPU, RAM, SSD가 보드에 존재하고

CPU는 느린 SSD와 직접 통신하지 않음

프로그램 실행 시, 데이터는 램으로 이동하고

CPU가 이를 가져감

RAM도 CPU보다 많이 느리기 때문에

CPU 내부나 근처에 캐시 메모리를 가지고 있음

캐시 메모리는 용량이 적으므로 중요한 데이터만 저장하여 사용

- CPU는 L1 -> L2 -> L3 -> RAM 순서로 원하는 데이터를 찾아봄

컴퓨터의 기억장치는 하드, 램, 캐시, 레지스터

- 레지스터 : CPU 내부에서 데이터를 일시적으로 저장하는 장치

레지스터 동작 원리와 종류 (일부)

- 프로그램 카운터(PC) : 다음에 수행할 메모리의 주소

- 메모리 주소 레지스터 : PC로부터 수행할 주소를 넘겨받고, 해당 주소에서 데이터를 가져옴

- 메모리 버퍼 레지스터 : 메모리 주소 레지스터가 가져온 데이터나 명령을 일시적으로 저장

해당 메모리가 명령어 일 경우 명령어 레지스터로 전달하고

연산에 사용될 데이터인 경우 누산기 레지스터로 전달

- 명령어 레지스터 : 명령에 관한 데이터 저장

- 제어장치 : 명령어 레지스터에게 명령을 받아 해석하고 시스템에 지시를 보냄

- 누산기 레지스터 : 연산의 결과나 중간 값을 일시적으로 저장

최종 결과는 메모리 버퍼 레지스터로 전달되고, 메모리 버퍼 레지스터를 통해 메모리로 전달됨

- ALU : 산술 논리 연산을 수행

개발자가 프로그래밍 언어로 개발한 프로그램은

컴파일되어 어셈블리어로 변환됨

어셈블리어는 어셈블러에 의해 0과 1로 된 기계어로 다시 변환됨

앞의 명령어 부분은 6bit로 이루어짐

뒤의 데이터 부분은 10bit로 이루어짐

프로세서가 한 번에 처리할 수 있는 값이 16비트가 됨

여기서 프로세서가 한번에 처리할 수 있는 단위는 워드(Word) 라고함

(32bit CPU의 워드 : 32bit[4byte])

(64bit CPU의 워드 : 64bit[8byte])

따라서 각 범용 레지스터의 크기는 워드의 크기만큼 정해짐

32bit CPU의 PC 레지스터의 크기 : 4byte

64bit CPU의 PC 레지스터의 크기 : 8byte

32bit가 표현할 수 있는 숫자는 2^32이다

따라서, 메모리의 주소도 2^32개만큼 표시할 수 있다

램의 각 주소 당 기본 메모리 단위는 1 byte 이므로

1byte를 2^32개 만큼 가리킬 수 있으며

이는 1byte * 2^32 = 4GB가 된다

즉, 32bit CPU는 최대 4GB의 표현하고 사용할 수 있다

실제로는 메모리에 컴퓨터 운영을 위한

다른 데이터도 올라가기 때문에 3GB 정도를 사용할 수 있다

이와 같이 64bit OS는 2^64인 16 엑사바이트만큼의 메모리를 표시하나?

그만큼의 메모리 어드레싱을 할 필요가 없기 때문에

실제로는 하위 48bit만 사용

다시 돌아와서 16bit CPU 예를 보자

해당 기계어는 램에 위와 같이 저장됨

램은 8비트씩 저장하므로 두줄로 저장

PC가 다음에 수행할 주소인 램의 100번 주소를 가리키고

메모리 주소 레지스터는 해당 명령 수행을 위해 100번 주소를 PC로부터 읽어옴

메모리 버퍼 레지스터는 100번째 주소의 값을 읽어와 저장

이 단계를 '인출'이라고 함

메모리 버퍼 레지스터에 저장된 데이터는 명령이기 때문에

명령어 레지스터에 저장

PC는 1 Word 만큼 증가(16bit CPU이므로 2byte만큼)

- 100 -> 102

명령어 레지스터에 저장된 명령은 제어장치로 이동되어 해석

이 단계를 '해석'이라고 함

제어장치의 명령은 10번째 데이터를 읽어 오는 명령이며

메모리 주소 레지스터에 읽어올 메모리의 주소(10번)가 저장되고

해당 주소(10번)에서 값을 읽어 메모리 버퍼 레지스터에 저장

10번 주소의 값은 명령어가 아닌 값(2)이므로 누산기 레지스터에 저장됨

여기까지가 명령어 LOAD[10] 한 줄의 처리 과정!

다음 처리를 위해 PC에 저장된 다음 실행할 주소(102)를 메모리 주소 레지스터로 가져옴

메모리 버퍼 레지스터를 통해 해당 값을 읽어오고

해당 값은 명령어이기 때문에 명령어 레지스터로 저장

명령어 레지스터의 명령 수행을 위해 제어장치로 저장

ADD 명령을 수행하기 위해 기존 누산기 레지스터의 값 2는

ALU로 전달

11의 값을 읽기 위해 메모리 주소 레지스터에 저장되고

읽어온 값은 메모리 버퍼 레지스터에 저장

해당 값(3)은 명령이 아닌 값이므로 바로 누산기 레지스터에 저장

ALU에 의해 바로 2 + 3이 수행되고 값은 누산기 레지스터에 다시 저장

이 단계를 '실행'이라고 함

모든 과정은 제어장치를 통해 컨트롤됨

마지막으로 PC에 저장된 104번째 명령을 처리하기 위해

메모리 주소 레지스터가 104를 저장하고

메모리 버퍼 레지스터가 해당 주소의 값을 읽어옴

해당 값은 STORE[12]인 명령어 이므로

명령어 레지스터에 저장됨

저장하라는 명령이 제어장치에 저장

해당 명령 수행을 위해 메모리 주소 레지스터에 저장할 주소(12)가 저장

누산기 레지스터에 저장된 5가 메모리 버퍼 레지스터에 저장

해당 값이 지정된 주소(12)의 메모리에 저장

이와 같이 CPU는 인출 -> 해석 -> 실행 -> 저장하는 과정을 거침

각 과정은 여러 개의 쓰레드에 의해 처리되며

코어 하나에 여러 개의 쓰레드가 실행되면 속도가 빨라지고

코어가 많아지면 더 빨라진다~

아키텍처 디자인은 회사마다 다르며

팬티엄, 샌디브릿지, 하스웰, 타이거레이크 등

다양한 형태로 진화하고 있음

여기까지 정리해봅니다

학부생 때 연구실에서 WSN(Wireless Sensor Network)를 공부하였고

당시에 선배들의 가르침으로 각 기기의 회사가 제공하는 DataSheet에 따라

센서나 통신 장비가 동작하도록 회로를 구성할줄은 알았지만

내가 한땜질이 어떻게 동작하는지 내부적으로 너무 궁금했습니다

논리회로 책을 따로 사서 공부해보았고

당시 트랜지스터가 어떻게 동작하는지 이해가 안가서 반도체 공부까지 했었습니다

재밌게도 영상에 이런 노고들을 종합해 잘 설명해놨네요

(당시에 봤으면 더 편했을텐데ㅋㅋ)

논리회로 -> 반도체 이론 -> 컴퓨터 구조

내용이 전반적인 이해로 이어지는 설명이 마음에 들어 내용 보충하여 정리해봤습니다

큰맘먹고 정리해놨으니 종종 읽어볼 만하지 않나 생각해봅니다ㅎㅎ

참고한 영상입니다

https://www.youtube.com/watch?v=Fg00LN30Ezg

'Tech > Other' 카테고리의 다른 글

| JOSE(JSON Object Signing and Encryption) (4) | 2022.07.20 |

|---|---|

| GitHub Copilot 후기 (0) | 2021.11.26 |

| vMotion(Live Migration) (0) | 2021.11.23 |

| Duplex, Duplication(이중화) (0) | 2021.10.26 |